Xilinx公司的FPGA中不仅有“成吨”的逻辑资源(slice),另外存储器、I/O、时钟和集成式IP资源也非常丰富,笔者在设计中经常使用Block RAM(BRAM)、DSP资源,灵活运用BRAM和DSP能为设计的速度和面积都带来一定的提升,可谓是鱼和熊掌兼得。

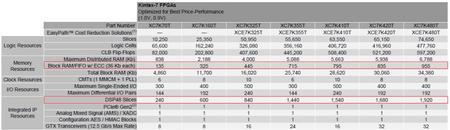

以Kintex-7系列为例,如图1所示为kintex-7各芯片资源表,其中Block RAM/FIFO w/ ECC (36 Kb each)和DSP48 Slices栏分别是BRAM和DSP资源数量,在FPGA项目初期,芯片选型时,需要参考此表进行资源评估。

图1

下面分别介绍一下Kintex-7系列FPGA中BRAM和DSP资源的使用:

1. BRAM

Kintex-7中BRAM块大小为36Kbit,也可以配置成两块18Kbit RAM,如FPGA设计中不同模块分别使用了一块18Kbit RAM,vivado软件会将这部分在一块BRAM中实现。

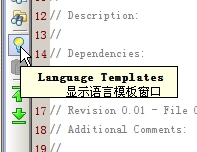

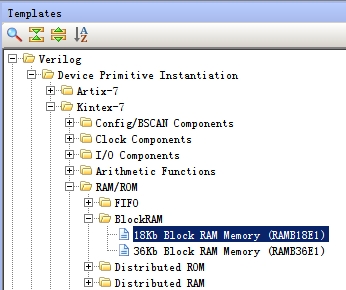

在FPGA设计中可采用多种方式调用BRAM,最常用的就是Core Generater工具,而笔者习惯于使用BRAM原语,将其根据需求自定义封装,最终在设计中类似以IP Core的形式例化BRAM,此方法的好处就是BRAM可以根据设计者的需求灵活配置。如图2、3所示,打开vivado的代码编辑器,在Language Templates中可以找到BRAM的原语,封装时只需拷贝出来即可。

图2

图3

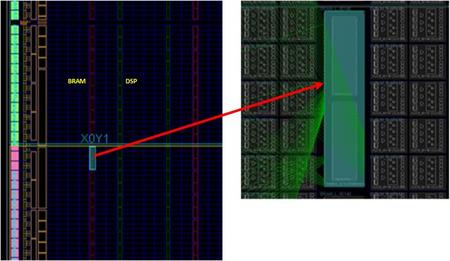

如代码见附件,笔者将BRAM原语封装后,经过vivado软件综合实现,在FPGA芯片中的布局实现如图4所示,BRAM、DSP在FPGA芯片中是按列布局的,其中红色列为BRAM,绿色列为DSP。

图4

2. DSP

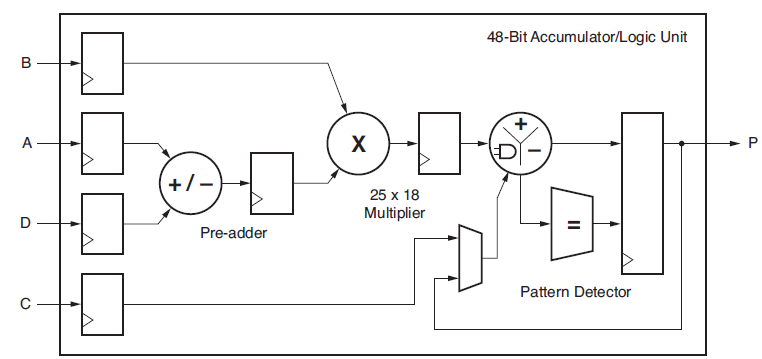

不仅Kintex-7,全7系列FPGA(Artix、Kintex、Virtex)中带有的DSP资源都是DSP48E1,其基本结构如图5所示,主要由预加器(Pre-adder)、乘法器(Multiplier)、累加器/逻辑单元(Accumulator/Logic Unit)和模式检测器(Pattern Detector),

图5

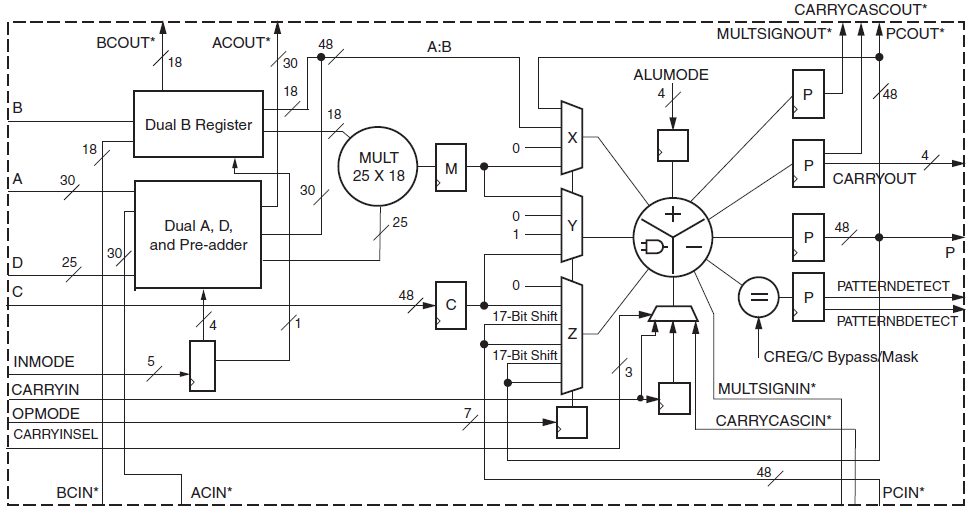

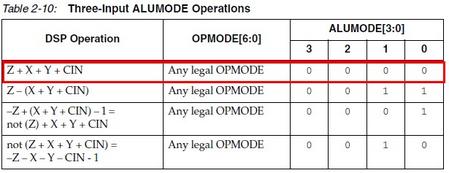

内部的详细结构如图6所示,其中预加器输入来自输入端口A(30-Bit)和D(25-Bit);乘法器的输入来自输入端口B(18-Bit)和预加器结果(25-Bit),支持25-Bit X 18-Bit的运算;累加器/逻辑单元的输入来自乘法器结果和输入端口C(48-Bit),输入的模式组合由控制字OPMODE决定,运算模式由控制字ALUMODE决定。

图6

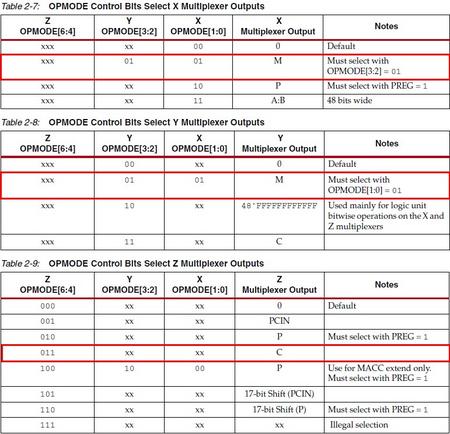

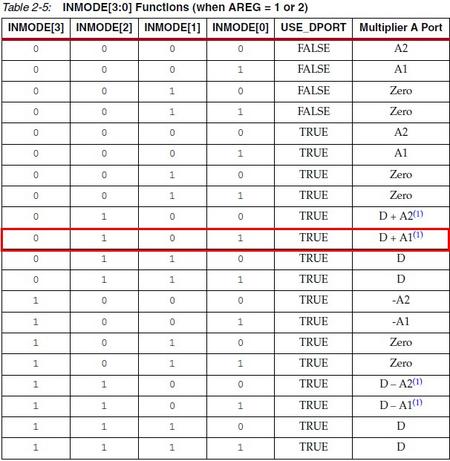

与BRAM类似,笔者通常采用封装原语的方式使用DSP48E1,在Language Template中选择48-bit Multi-Functional Arithmetic Block,然后根据需求配置参数,如需得到P=(A+D) x B + C,其中各参数配置需要根据DSP48E1的datasheet进行配置:

如图7红框中配置,OPMODE=7‘b0110101

图7

如图8红框中配置,INMODE=4’b0101

图8

如图9红框中配置,ALUMODE=4‘b0000

图9

封装代码见附件,经过vivado软件综合实现后,类似于图4,布局在DSP列中。

/5

/5

用户1017176 2014-3-23 04:48