在“BRAM和DSP间的纠缠(一)”中介绍了Xilinx FPGA中BRAM和DSP的使用,可能大家会奇怪为什么博文标题中会有“纠缠”二字,那在本文中将会详细道来。

笔者在FPGA项目中多次遇到一个问题:设计中关键路径在BRAM和DSP之间。也许有读者会问,是不是BRAM和DSP之间没有寄存器分割路径?答案是有,输出寄存、输入也寄存了,至于为什么产生这个问题,请看以下分析:

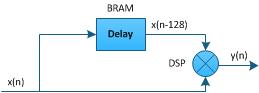

以一个简单设计为例,结构如图1所示,算法也一目了然y(n)=x(n)*x(n-128),其中BRAM延时128个时钟,DSP作为乘法单元。

图1

顶层Verilog代码如下,其中bram_delay和mult分别为封装BRAM原语和DSP48E1原语后的模块,模块代码见附件。

以下是代码片段:

图2

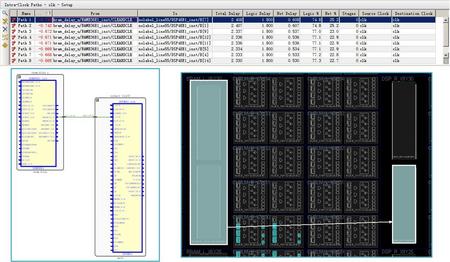

详细的关键路径报告如图3所示,在Data Path由两部分组成:RAMB36E1(Prop ramb36e1 CLKARDCLK DOADO[7])和net(fo=1, routed)。前者属于BRAM输出寄存器的clock_to_out延时,而后者属于布线延时,显然这个布线延时0.608ns过大,对于491MHz时钟频率下只有2.037ns的余量的情况下。另外当前设计只是时钟频率较高,在设计资源紧缺的情况下,布局不可能如此好,BRAM和DSP是紧挨着的两列布局,因此实际情况中这段布线延时至少会大于0.608ns。

图3

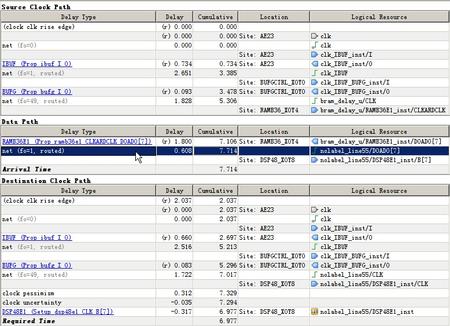

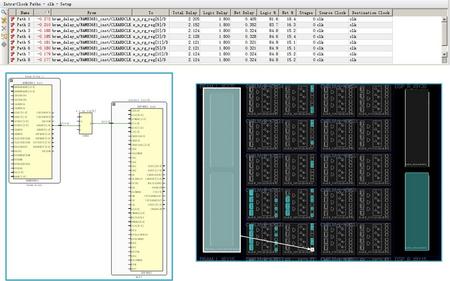

以上算是复现了问题,究其问题的原因是布线过长,布线过长是因为没有寄存器分割,但是BRAM和DSP之间是有寄存器分割的呀,只不过寄存器是在BRAM和DSP内部,而BRAM和DSP的布局位置被限制在资源列中,布局不是那么灵活,至此答案已经很清晰了,只要中间再加入一级寄存器(slice实现)分割路径即可,修改后的顶层Verilog实现代码如下,由于多了一级延时,相应的在BRAM中需要减少一级延时:

以下是代码片段:

图4

综上,这“纠缠”和解“纠缠”讲诉完毕,这边需要说明一下,这问题不一定适用于所有情况,在低速设计中或者资源不紧张的情况下此问题可以完全忽略。

/5

/5

文章评论(0条评论)

登录后参与讨论