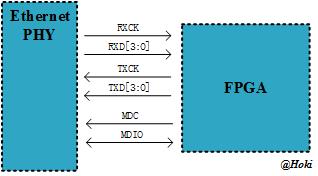

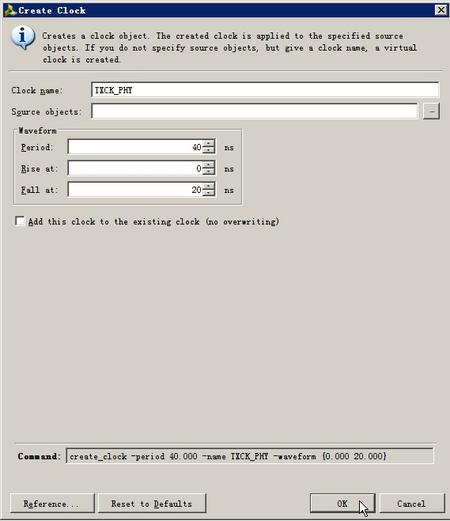

本节讲解一下output delay的实例。依旧是Ethernet PHY和FPGA的接口,框图如图1所示,其中TX接口,MII管理接口输出方向需要output delay约束。

图1

TX接口:

TX接口由时钟TXCK和数据TXD[3:0]组成,都是从FPGA输出,即时钟和数据同源,因此TX接口为源同步输出接口。

根据上节中output delay value的计算公式:

max_input_delay = Tbd_max + Tsetup - Tcd_min

min_input_delay = Tbd_min – Thold - Tcd_max

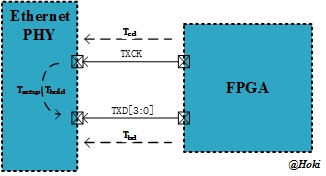

其中有4个时间参数:Tbd,Tcd,Tsetup和Thold,如图2所示。

图2

Tcd和Tbd分别是时钟TXCK和数据TXD[3:0]在板上的延时。首先通过PCB设计软件计算得到它们布线长度:LTXCK=784mil,LTXD[3]=663mil,LTXD[2]=680mil,LTXD[1]=852mil,LTXD[0]=901mil,因此计算得到:

Tcd_max= Tcd_min=784mil*166ps/inch= 0.130144ns

Tbd_max=901mil*166ps/inch=0.149566ns, Tbd_min=663mil*166ps/inch=0.110058ns

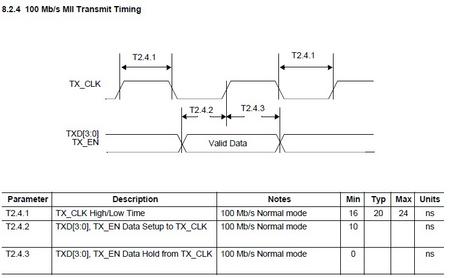

Tsetup和Thold是PHY(DP83849ID)芯片的时间参数,如图3所示,查询datasheet得到:

参考时间参数T2.4.2,Tsetup=10ns

参考时间参数T2.4.3,Thold=0ns

图3

综上可得到output delay value:

max_output_delay = Tbd_max + Tsetup - Tcd_min=0.149566ns + 10ns - 0.130144ns=10.019422ns

min_output_delay = Tbd_min – Thold - Tcd_max=0.110058ns – 0ns - 0.130144ns=-0.020086ns

可能有些人会诧异,为什么min_output_delay的值会是负的?负的表示相对于输出是反方向的延时。

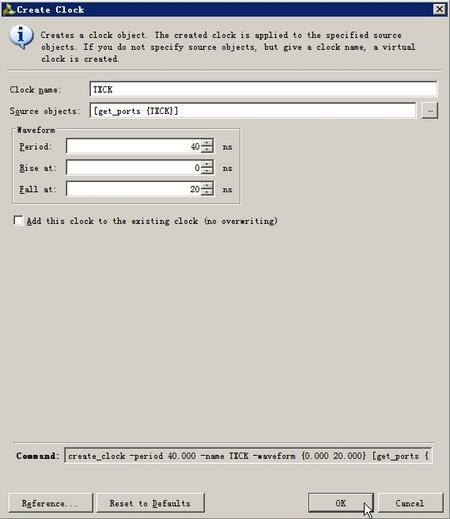

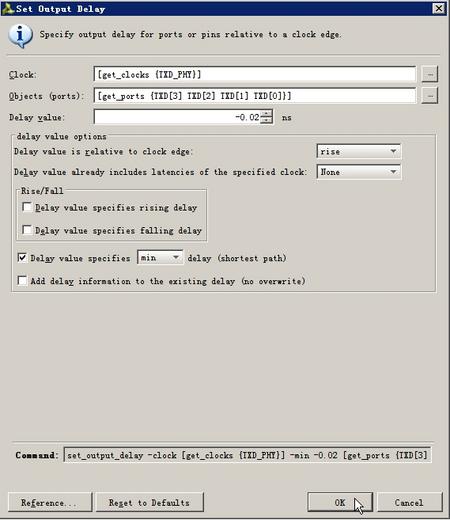

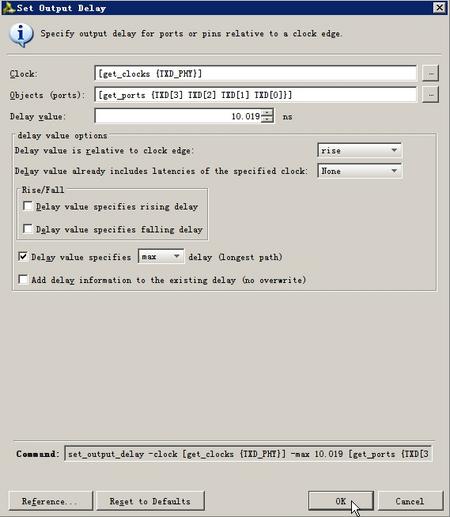

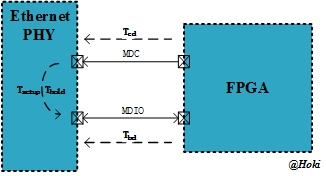

下面对TX接口的output delay进行约束:

create_clock -name TXCK -period 40 -waveform {0 20} [get_ports {TXCK}]

create_clock -name TXCK_PHY -period 40 -waveform {0 20}

set_output_delay –clock TXCK_PHY -max 10.019422 [get_ports {TXD[3] TXD[2] TXD[1] TXD[0]}]

set_output_delay –clock TXCK_PHY -min -0.020086ns [get_ports {TXD[3] TXD[2] TXD[1] TXD[0]}]

Vivado中约束如下图所示:

约束主时钟

约束虚拟时钟

约束min output delay

约束max output delay

MII管理接口:

MII管理接口由时钟MDC和数据MDIO组成,其中MDIO为双向接口,因此需要对其进行input delay和output delay约束。在其output方向,MDC和MDIO都是从FPGA输出的,因此也是源同步输出接口。

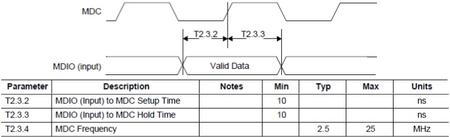

时间参数的计算与TX接口类似,如图4所示

图4

其中MDC和MDIO在板上的布线长度分别为LMDC=924mil,LMDIO=587mil,可得:

Tcd_max= Tcd_min=924mil*166ps/inch= 0.153384ns

Tbd_max=Tbd_min=587mil*166ps/inch=0.097442ns

Tsetup和Thold的值参考datasheet,如图5所示,可得:

参考时间参数T2.3.2,Tsetup=10ns

参考时间参数T2.3.3,Thold=10ns

图5

综上可得到output delay value:

max_output_delay = Tbd_max + Tsetup - Tcd_min=0.153384ns + 10ns - 0.097442ns=10.055942ns

min_output_delay = Tbd_min – Thold - Tcd_max=0.153384ns - 10ns - 0.097442ns=-9.944058ns

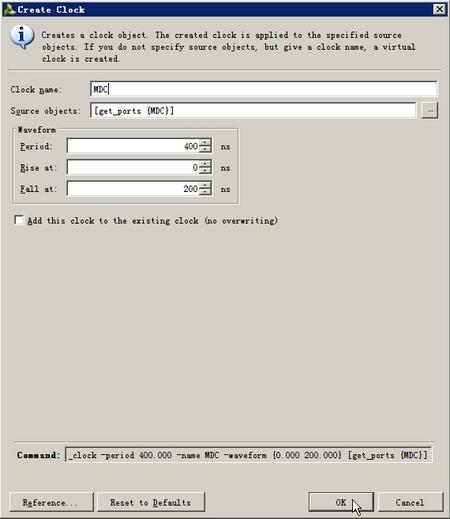

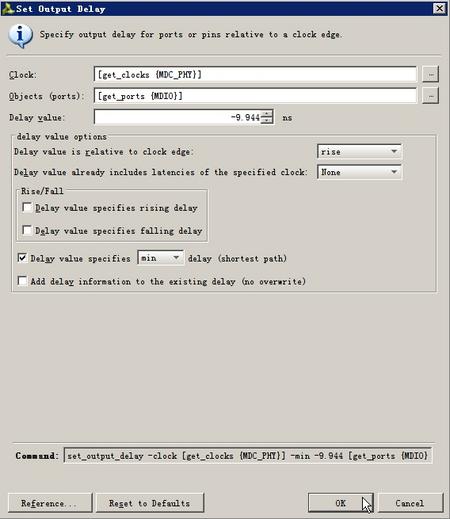

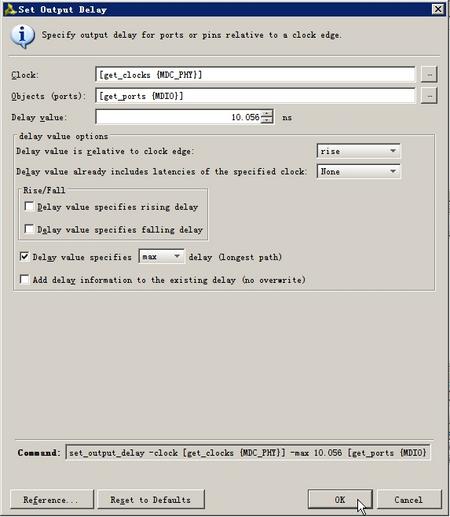

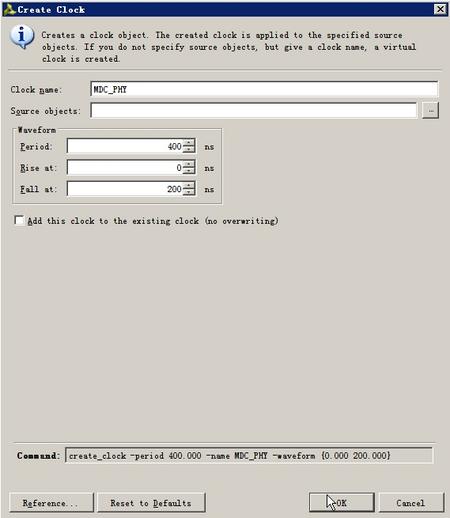

下面对MII管理接口的output delay进行约束:

create_clock -name MDC -period 400 -waveform {0 200} [get_ports {MDC}]

create_clock -name MDC_PHY -period 400 -waveform {0 200}

set_output_delay –clock MDC_PHY -max 10.055942 [get_ports {MDIO}]

set_output_delay –clock MDC_PHY -min -9.944058 [get_ports {MDIO}]

Vivado中约束如下图所示:

约束主时钟

约束虚拟时钟

约束max output delay

约束min output delay

/2

/2

文章评论(0条评论)

登录后参与讨论