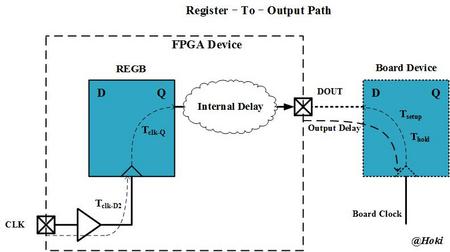

FPGA内部时序单元到输出端口的路径也需要约束其output delay,如图1所示框图。

图1

约束output delay的命令是set_output_delay,具体的参数如下:

set_output_delay –clock reference_clock –min/-max delay_value [get_ports {DOUT}] [-clock_fall] [-add_delay]

其中-clock表示输出端口的关联时钟;

-min/-max表示设置output delay的最小和最大值;

-clock_fall表示output delay是针对关联时钟的下降沿;

-add_delay表示对同一个输出端口约束不同的output delay值,一般是在如DDR需要约束两个时钟沿的output delay,或者输出端口后级连接了多个器件对应不同的时钟约束的情况下,需要加入此参数。

与输入接口约束类似,输出接口的约束也可分为以下两种情况:

1. System Synchronous Output

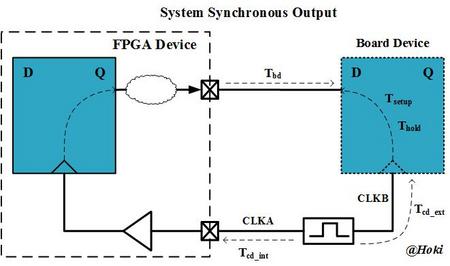

分析FPGA内部时序单元到输出端口的路径时,当source clock和destination clock来自同一个系统时钟时,称为系统同步输出(system synchronous output)。

此处需要引入虚拟时钟(virtual clock)的概念,在讲时钟约束的一节时有提到,当source clock or destination clock不在FPGA设计中时,则需要约束一个虚拟时钟。如图2所示为系统同步输出路径框图,source clock是CLKA,destination clock是CLKB,其中CLKA通过输入端口引入FPGA内部(约束成主时钟),而CLKB引到了FPGA外部的板上芯片,并没有引入到FPGA内部,因此需将CLKB约束成虚拟时钟,约束如下:

create_clock -name CLKA -period 10 -waveform {0 5} [get_ports {CLKA}]

create_clock -name CLKB -period 10 -waveform {0 5}

图2

其中Tcd_ext表示外部时钟源到外部芯片的延时;Tcd_int表示外部时钟源到FPGA时钟端口的延时;Tsetup表示外部芯片tsu时间;Thold表示外部芯片thd时间;Tbd表示FPGA输出端口到外部芯片的板上延时。

Output delay value的计算式如下:

max_output_delay = Tbd_max + Tsetup + Tcd_int_max - Tcd_ext_min

min_output_delay = Tbd_min – Thold + Tcd_int_min - Tcd_ext_max

相比于input delay value,上式相对于难理解些,那就推导一下,深入理解:

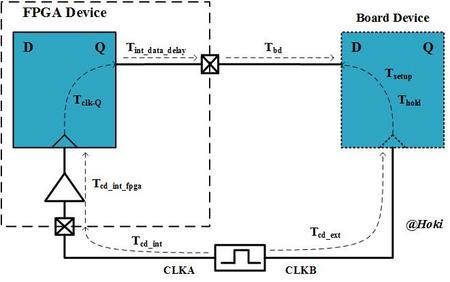

将此路径假想为FPGA内部register_to_register路径作分析,如图3所示,

图3

在《2. Timing Basics》节中,介绍了时序分析分为Setup Check和Hold Check:

Setup Check

setup slack = (destination clock edge time - source edge time)

+ (destination clock path delay - source clock path delay)

- clock uncertainty - setup time - clock to output time - data path delay

将图3中路径的时间参数代入可得:

setup slack = Tclk_period + (Tcd_ext – Tcd_int – Tcd_int_fpga) – Tclk_uncertainty – Tsetup – Tclk-Q – Tint_data_delay - Tbd

其中Tcd_ext,Tcd_int,Tsetup和Tbd都是FPGA外部的时间参数,需要通过约束告知vivado,上式整理一下可得:

setup slack = Tclk_period – Tcd_int_fpga – Tclk_uncertainty – Tclk-Q – Tint_data_delay + (Tcd_ext – Tcd_int) – Tsetup - Tbd = Tclk_period – Tcd_int_fpga – Tclk_uncertainty – Tclk-Q – Tint_data_delay – Tmax_output_delay

Tmax_output_delay = Tsetup + Tbd_max + Tcd_int_max - Tcd_ext_min,与前文中max_output_delay的计算式相同。

Hold Check

hold slack = (source clock edge time - destination edge time)+(source clock path delay - destination clock path delay) - clock uncertainty - hold time + clock to output time + data path delay

= (Tcd_int + Tcd_int_fpga - Tcd_ext) - Tclk_uncertainty – Thold + Tclk-Q + Tint_data_delay + Tbd

其中Tcd_ext,Tcd_int,Thold和Tbd都是FPGA外部的时间参数,需要通过约束告知vivado,上式整理一下可得:

hold slack = Tcd_int_fpga - Tclk_uncertainty + Tclk-Q + Tint_data_delay + Tbd – Thold + Tcd_int - Tcd_ext

= Tcd_int_fpga - Tclk_uncertainty + Tclk-Q + Tint_data_delay + Tmin_output_delay

Tmin_output_delay = Tbd_min – Thold + Tcd_int_min - Tcd_ext_max,与前文中min_output_delay的计算式相同。

可以发现在setup check中使用max output delay,hold check使用min output delay,都是使slack的值较小的趋势,这样使FPGA内部的时序条件更严苛,如果在这种条件下时序收敛,就绝对能保证设计的稳定性。

经过上面的推导,回归系统同步输出主题,约束命令如下:

set_output_delay -clock CLKB -max max_output_delay [get_ports {DOUT}]

set_output_delay -clock CLKB -min min_output_delay [get_ports {DOUT}]

2. Source Synchronous Output

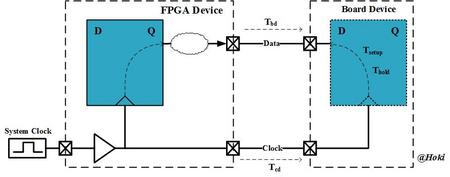

分析FPGA内部时序单元到输出端口的路径时,输出到外部芯片的时钟与数据是同源的,称为源同步输出(source synchronous output)。

结构如图4所示,从FPGA输出到外部芯片除了有数据,还有一个随路时钟,由FPGA内部时钟模块产生的。

图4

参考图4中时间参数,其中Tcd表示时钟从FPGA输出到外部芯片输入端口的延时;Tsetup表示外部芯片tSU时间;Thold表示外部芯片tH时间;Tbd表示FPGA输出端口到外部芯片的板上延时。Output delay的计算式如下(推导与系统同步输出类似,不再累述):

max_output_delay = Tbd_max + Tsetup - Tcd_min

min_output_delay = Tbd_min – Thold - Tcd_max

源同步输出的output delay约束命令如下:

set_output_delay -clock CLKB -max max_output_delay [get_ports {DOUT}]

set_output_delay -clock CLKB -min min_output_delay [get_ports {DOUT}]

/4

/4

文章评论(0条评论)

登录后参与讨论