数字信号处理,我们简称DSP,大家和硬件DSP先做个区分。最开始我们使用的系统都是模拟系统,像这个第一代移动通信系统,我们最开始使用的模拟的电视,还是黑白的,后面还驮了好大的一个显像管。后来随着数字时代的到来,很多模拟系统,模拟产品都转向数字化,手机也不用弄一个板砖样的模拟接收器,转向了第二代移动通信系统,电视也不用因显像管占用很大的空间,方便到用挂式。这些都是因为数字系统相比模拟系统来讲有一下几大优点:

(1) 抗干扰性强;

(2) 便于进行各种数字信号处理;

(3) 易于实现集成化;

(4) 经济效益超过模拟通信

(5) 传输与交换可结合起来,传输电话与传输数据也可以结合起来,成为一个统一体,有利于实现综合业务通信网;

(6) 便于多路复用;

数字系统虽然有这些优点,但是我们实际传送过程中还都是模拟信号,包括最开始的信号来源,和最终传送发送出去的信号都是模拟信号。所以我们要进行数字处理,就必须采用两种器件将我们这个模拟世界和数字世界给连接起来,这两种器件分别是模数转换器ADC和数模转换器DAC。我们可以得到典型的数字信号处理的一个模型,如图。

模数转化器ADC周期性的对输入的模拟信号采样,并做量化,其实ADC是由采样保持和量化编码器构成的。采样需要满足内奎斯特采样定理,采样位宽数和采样速率决定了后期数字信号处理的精度。

采样得到的数字数据后,开始在做DSP处理了,应用不同,处理的算法和过程就不一样,目前数字信号可以干的事情可以列表如表。

数字信号处理应用

|

应用领域 |

DSP算法 |

|

通用领域 |

自适应滤波、滤波和卷积、检测和纠正、谱估计和傅立叶变换 |

|

语音处理 |

编码和解码、加密和解密、语音识别和合成、扬声器识别、回声消除、人工耳蜗的信号处理 |

|

音频处理 |

hi-hi编解码、噪声消除、音频平衡、环境声学仿真、混音和编辑、声音合成 |

|

图像处理 |

压缩和解压缩、旋转、图像传输与分解、图像识别、图像增强、人工视网膜的信号处理 |

|

信息系统 |

语音信箱、传真、调制解调器、移动电话、线路均衡器、数据加密和解密、数字通信和局域网、延拓频谱技术、无线局域网、广播电视、生物医学信号处理 |

|

仪表设备 |

波束成型、波形发生器、瞬态分析、稳态分析、科学仪器设备、雷达和声纳 |

从表中可以看出,广泛的看几乎是采用数字的系统和产品应用里都涉及到数字信号的处理,包括表中还列出了前面我们讲到的通信领域和视频图像处理领域相关的应用,同时表中列出了通用领域的一些算法,这是数字信号处理较普遍性、较专对性的。

经过数字信号处理之后,得到的仍然是数字信号,数模转换器DAC将会对这些数字信号进行模拟化后发送出去,在通信过程中一般是在射频或是中频做这个处理。

讲到数字信号处理的实现方式很多人的第一反映就是数字信号处理器,就是我们这个硬件DSP。没错它是一个专门做数字信号处理的,但是做除此之外,其实还有几种做数字信号处理的方式,所以在本节最开始的时候就讲到大家要区分一下我们这里数字信号处理DSP和数字信号处理器DSP,以免内心一直存在这么一个纠结的问题影响这一节的学习。除了专用的硬件DSP外,通用微处理器、专用的ASIC硬件、还有专用的FPGA也可以做数字信号处理。我们来一一分析一下。

首先是通用微处理器,也可以称为中央处理器(CPU)或者微处理器(MPU),通过在处理器中运行适当的DSP算法可以执行DSP任务。特别是在近几年来很火的GPU,这个专门做图像处理的处理器里,它内部采用很多个处理器并行操作,在数字图像的相关处理可谓相当的专业,在一些高端显卡里面一般都配置有GPU。

其次是专用的ASIC硬件,这一块主要是客户化的执行DSP任务的硬件实现,相对来说,实现的功能单一,只能实现实现定义好的功能。这一类的器件比如数字滤波器芯片、数码相机里的专用图像处理芯片等等。但是优点是功能经过全面的验证,并优化后,做成ASIC化,运行非常稳定,速度也非常快。

第三种就是专用的数字信号处理器,它是一种特殊的微处理器芯片,经过了专门的设计,执行DSP任务时比通用的微处理器要快更高效,同时也比专用ASIC更加灵活。那么它特殊在哪里呢?

在我们上一小节列举的那些DSP算法中,有一个共同地方就是,需要大量的乘法和加法来完成,再怎么复杂的算法也都是有许许多多的这样的乘加来构成的。而乘法在硬件里用逻辑来搭建的话不管是面积上还是速度性能上都不是很理想,在通用的微处理器里,即使有硬件乘法器,数量也是有限,做其复杂算法来,速度性能上还是欠佳。于是硬件DSP这样拥有大量的乘加结构的处理器出现了,这就是它的特殊之处。尽管是专门做数字信号处理的器件,但是它依然存在问题,针对它的开发依然是基于串行的任务队列的软件模式开发,效率和灵活性依然有限。

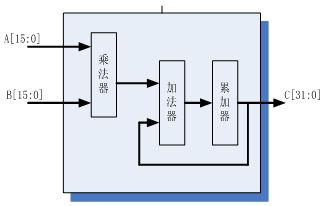

第四种就是专用的FPAG硬件,刚才我们有讲到列举的那些DSP算法的一个共同特点是大量用到乘加操作,如果想要把DSP算法做好,确实是需要这些做这些乘加操作的硬件支持。细心的读者会发现,这里说的是专用的FPGA硬件,这里和之前在FPGA原理里提到的各种FPGA并没有很大的出路,只是在它们的基础上再添加了这些专用用来做DSP的乘加硬件,如图XX,

用FPGA来做数字信号处理的好处在于,完全是硬件化并行化编程操作,可以在速度和面积之间的转变有很大的灵活性,在下一节里我们将通过一个例子来看看它的体现。

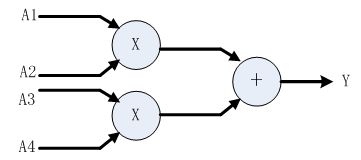

这里给出DSP处理的最基本的乘加例子,实现的算方表达式如下:

采用FPGA的并行机制,假设乘法器都是并行操作,我们得到如图实现的电路。从图上我们看到,这种方式执行的时间相当与一个乘法器和一个加法器实现的时间,速度非常快,但是他却消耗了两个乘法器和一个加法器。

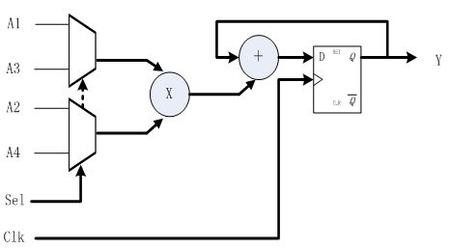

由于FPGA的编程的灵活性,我们也可以采用资源共享的方式来得到一个串行的实现电路,如图XX所示,在图中可以看到,它消耗了两个二选一多路器、一个乘法器、一个加法器和一个寄发器。虽然多了两个二选一多路器和一个触发器,但是这资源比乘法器的资源还是节约了不少。但是它的速度就降下来了,通过开关Sel来控制,先做A1和A2的乘法,结果在时钟驱动下保留在寄存器中,然后翻转Sel,再做A3和A4的乘法,结果和上次运行的存放在寄存器中的结果做加法,在第二个时钟驱动下存储最终结果。这样共享用一个乘法器,速度相比第一种情况慢,好的地方就是节约了面积。但是需要提的是,即使是这样的共享式的实现速度也会比DSP专用芯片的软实现速度要快。

相比之下得出,采用专用的FPGA做DSP,不但可以在速度和面积上灵活调节,至少实现速度还是比专用的DSP要快一点。通常我们很多场合,专用DSP的使用还是如日中天,一个原因是我们专用的FPGA的做DSP的资源还不是很富足,二个原因是专用DSP的开发采用的是软件式开发,而FPGA采用的是硬件开发,这对很多工程师来讲还是会选择前者的,第三个原因是这个成本问题,毕竟传统的专用的DSP芯片比专用的FPGA芯片要便宜。

各FPGA厂商对数字信号处理的资源支持还是比较强大的,这包括前面提到的在通信领域和图像处理领域提供的支持资源,有相关的IP核、相关的使用工具和一些参考设计方案,这里我们就不再重复,只是做一些补充。

表Xilinx 其他DSP IP核

|

分类 |

IP核 |

描述 |

|

滤波器 |

CIC Compiler |

The Xilinx CIC Compiler LogiCORE is a module for design and implementation of Cascaded Integrator-Comb (CIC) filters for a variety of Xilinx FPGA devices |

|

DUC/DDC Compiler |

Digital Up/Down Converters (DUC/DDC) are important components in the signal processing chains of many digital communications systems. The Xilinx DUC/DDC Compiler LogiCORE provides users with means to rapidly implement these functions for a range of wireless interface standards based on system-level parameters. The core implementation is delivered through the Xilinx CORE Generator system, and is designed to take advantage of the advanced features of Xilinx FPGA devices |

|

|

FIR Compiler |

The Xilinx FIR Compiler LogiCORE is a module for generation of high speed, compact filter implementations that can be configured to implement many different filtering functions. The core is fully synchronous, using a single clock, and is highly parameterizable, allowing designers to control the filter type, data and coefficient widths, the number of filter taps, the number of channels, etc. Multi-rate operation is supported. The implementation method can be specified by the user, with a choice of Multiply-Accumulate or Distributed Arithmetic architectures. The core is delivered through the Xilinx CORE Generator System and integrates seamlessly with the Xilinx design flow |

|

|

变换 |

Discrete Fourier Transform |

The Discrete Fourier Transform (DFT) core has been specifically designed to meet the needs of the LTE standard, in terms of point sizes, low latency and resource requirements. |

|

Fast Fourier Transform |

The Fast Fourier Transform (FFT) is a computationally efficient algorithm for computing the Discrete Fourier Transform (DFT). The FFT Core can compute 8 to 65536-point forward or inverse complex transforms on up to 12 parallel channels. The input data is a vector of complex values represented as two's-complement numbers 8 to 34 bits wide or single precision floating point numbers 32 bits wide. The phase factors can be 8 to 34 bits wide. All memory is on-chip using either Block RAM or Distributed RAM. Three arithmetic types are available: full-precision unscaled, scaled fixed-point, and block-floating point. Several parameters are run-time configurable: the point size, the choice of forward or inverse transform, and the scaling schedule. Four architectures are available to provide a tradeoff between size and transform time |

|

|

LTE Fast Fourier Transform |

The LTE Fast Fourier Transform LogiCORE(TM) implements all transform lengths required by the 3GPP LTE specification, including the 1536-point transform for 15 MHz bandwidths. The transform length, transform direction, cyclic prefix length and scaling schedule may be configured on a per-frame basis |

|

|

调制 |

DDS Compiler |

The Xilinx DDS Compiler LogiCORE provides Direct Digital Synthesizers (DDS) and optionally either Phase Generator or Sine/Cosine Lookup Table constituent parts as independent cores. The core features sine, cosine or quadrature outputs with 3 to 26-bit output sample precision. The core supports up to 16 channels by time-sharing the sine/cosine table which dramatically reduces the area requirement when multiple channels are needed. Phase Dithering and Taylor Series Correction options provide high dynamic range signals using minimal FPGA resources. In addition, the core has an optional phase offset capability, providing support for multiple synthesizers with precisely controlled phase differences |

|

块运算 |

Complex Multiplier |

Complex multiplication is a basic DSP operation. All operands, as well as the results, are represented as signed two's-complement data. Operand widths and result widths are parameterizable. Operand widths up to 63 bits are supported |

|

CORDIC |

The Xilinx CORDIC LogiCORE is a module for generation of the generalized coordinate rotational digital computer (CORDIC) algorithm which iteratively solves trigonometric, hyperbolic and square root equations. The core is fully synchronous using a single clock. Options include parameterizable data width and control signals. The core supports either serial architecture for minimal area implementations, or parallel architecture for speed optimization. The core is delivered through the Xilinx CORE Generator System and integrates seamlessly with the Xilinx design flow |

表Altera其他DSP IP核

|

分类 |

IP核 |

|

算法 |

Floating Point Megafunctions |

|

滤波和变换 |

|

|

FFT/IFFT |

|

|

FIR Compiler |

|

|

FIR Compiler II |

|

|

调制解调 |

Numerically Controlled Oscillator Compiler |

handong123123_906892115 2012-9-18 10:23

用户377235 2012-9-17 21:34

用户415298 2012-9-9 19:11

handong123123_906892115 2012-9-6 09:36

希望网友更多的关注产品设计的过程,尤其是设计计算部分,这才是文章的重点。

handong123123_906892115 2012-9-5 09:38

用户403664 2012-9-4 08:52