拿下变量数据类型

在上一讲中,我们讲了常量数据类型的语法介绍,从如何表达一个整数,x和z的意义,参数(parameter)型常量的使用到常量一些默认的规律。常量数据类型在verilog HDL是很重要的,那么变量数据类型呢? 答案是肯定的,变量数据类型甚至更重要。

其实是可以变很多的

什么是变量呢?在程序运行过程中可以改变的量就是变量。既然是变量,那肯定是可以变出很多数据类型啊,总体来说有两大派系,一是网络(net)连接类型,另一个是寄存器(Register)类型变量。

我们怎么区分这两大派系呢?网络(net)连接类型不能存储数据,就好比家家户户的普通的连接管;而寄存器(Register)类型变量可以存储数据,直至被赋予新值,好比带源头的管子。后面的具体的门派好比管子又有很多,比如自来水管、下水道管,通风管、北方的暖气管等

下面我们来细说这两大派系。

1.网络(net)连接类型

网络(net)连接类型变量是用于结构实体之间的物理连接,它不能存储数值,必须要有驱动器(例如:模块或门驱动,连续赋值语句)的驱动,驱动器信号的改变其驱动变量的数值,若没有驱动器的驱动其变量的就是高阻的,其值为z;在多驱动源的情况下,逻辑值会发生冲突,产生不确定的值。

那么派系有什么具体的门派呢?其主要的有wire型, tri型,supply0型, supply1型,wor型,trior型,wand型, triand型,trireg型,tri1型,tri0型等。

各个门派都是有什么绝技的呢?

wire, tri 型

此类变量主要用于连接单元的连线,是最常见的net类型变量。wire型变量通常用来表示单个驱动源驱动的net型变量,而tri型(用于建模仿真)变量通常用来表示多驱动器驱动的网络型数据。在不同的场合用不同的net类型,只是为了区分用的场合而已,而wire型与tri型语法和语义一致,可以相互替换。我们还是看个多驱动源的例子吧。

模块程序如下:

module or_test(

ain,

bin,

cout

);

input ain;

input bin;

output cout;

tri cout;

assign cout=bin;

assign cout=ain;

endmodule

上面的双驱动模块不可综合,但可以仿真,仿真结果想如下:

综合以后会有以下语法错误。

对上面的双驱动模块进行仿真,程序如下:

module testbench;

reg ain,bin; // Inputs

wire cout;

//实例化模块

or_test uuu (

.ain(ain),

.bin(bin),

.cout(cout)

);

initial begin

ain = 0;

bin = 0;

#10;

ain = 0;

bin = 1;

#10;

ain = 0;

bin = 1'bx;

#10;

ain = 0;

bin = 1'bz;

#10;

ain = 1;

bin = 0;

#10;

ain = 1;

bin = 1'bx;

#10;

ain = 1;

bin = 1'bz;

#10;

ain =1'b x;

bin = 1'bx;

#10;

ain = 1'bx;

bin = 1'bz;

#10;

ain = 1'bz;

bin = 1'bz;

#10;

$stop;

end

endmodule

下面仿真的结果

根据上面的仿真可以得出多驱动源时的真值表:

|

wire,tri |

0 |

1 |

X |

Z |

|

0 |

0 |

X |

X |

0 |

|

1 |

X |

1 |

X |

1 |

|

X |

X |

X |

X |

X |

|

Z |

0 |

1 |

X |

Z |

supply1, supply0型

supply0型变量用于对“地”建模,即低电平0;supply1型变量用于对电源建模,即高电平1。这类变量是可以综合的。例如:

module or_test(

cout,dout

);

output cout;

output dout;

supply0 ain; // supply0对应的地

supply1 bin; // supply1对应的地

assign dout=bin;

assign cout=ain;

endmodule

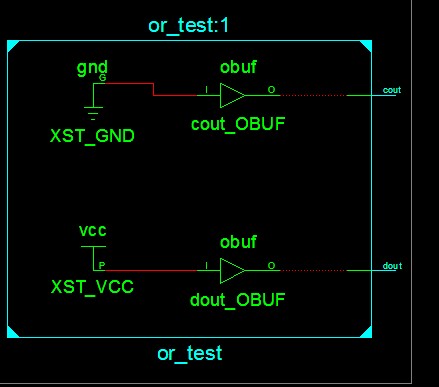

下图为综合出来的电路图,,supply1对应的是电源。

wor, trior型

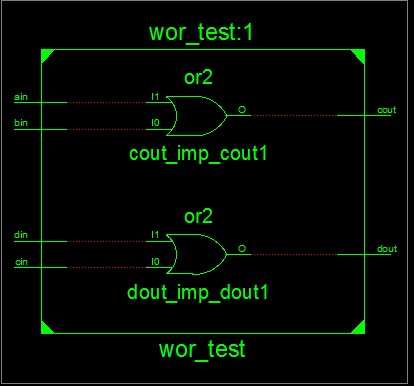

此类型数据对应于有多个驱动源的线或逻辑连接,综合出来的结果相当于或门。当有多个驱动源驱动线或(wor)和三态线或(trior)数据时,就会产生线或结构。线或(wor)和三态线或(trior)如果某个驱动源为1,这类变量的值也为1。

举个例子吧。

module wor_test(

ain, bin, cin, din, //in

cout, dout //out

);

input ain,bin,cin,din;

output cout,dout;

wor cout; //wor 类型声明

trior dout; //trior类型声明

assign cout=bin;

assign cout=ain; //wor 类型多驱动源

assign dout=cin;

assign dout=din; //trior类型多驱动源

endmodule

上面是一个用两个驱动源驱动一个wor型和tri型的变量,其综合出来的电路如下,从图可以看出,他就是一个双输入的或门电路。

大家可以仿照wire和tri型仿真程序进行仿真,根据仿真结果(大家可以自己做一下,篇幅有限,不在重复),同样可以得出多驱动源时的真值表:

|

wor,trior |

0 |

1 |

X |

Z |

|

0 |

0 |

1 |

X |

0 |

|

1 |

1 |

1 |

1 |

1 |

|

X |

X |

1 |

X |

X |

|

Z |

0 |

1 |

X |

Z |

wand, triand型

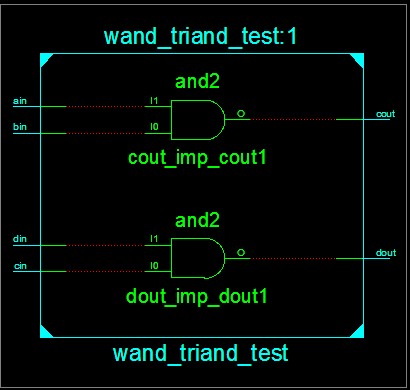

此类型数据对应于有多个驱动源的线与逻辑连接,综合出来的结果相当于与门。当有多个驱动源驱动线或(wand)和三态线或(triand)数据时,就会产生线与结构。线与(wand)和三态线与(triand)如果某个驱动源为0,这类变量的值也为0。比如:

module wand_triand_test(

ain, bin, cin, din, //in

cout, dout //out

);

input ain,bin,cin,din;

output cout,dout;

wand cout; //wand 类型声明

triand dout; //triand类型声明

assign cout=bin;

assign cout=ain; //wand 类型多驱动源

assign dout=cin;

assign dout=din; //triand类型多驱动源

endmodule

/5

/5

文章评论(0条评论)

登录后参与讨论