10.6关于case的约束

关于case的约束,主要有两种形式,一种是用verilog里面提供的primitive约束或者Synopsys提供的引导语句。不管用哪一种,都能起到对case约束的效果。

1.如何使用primitive约束

primitive约束主要有FULL_CASE, PARALLEL_CASE 两种,我们只需在case关键字添加

( * primitive 名称 * )即可,在综合时编译器默认为case 语句进行的相应的约束。

FULL_CASE,PARALLEL_CASE有什么神奇的功效呢?我们还是看带有个FULL_CASE约束例子吧。

input [1:0] sel,ain,bin;

output [1:0] out;

reg [1:0] out;

always @(sel or ain or bin)begin

(* FULL_CASE *) case(sel)

2'b01: out = ain;

2'b10: out = bin;

endcase

end

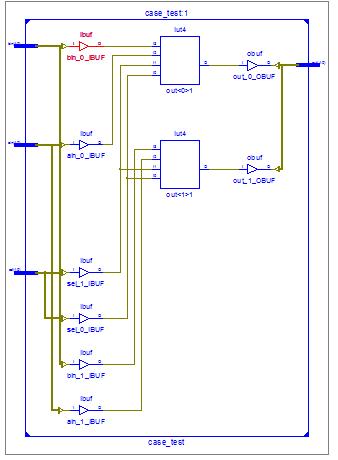

上面程序综合后的电路图

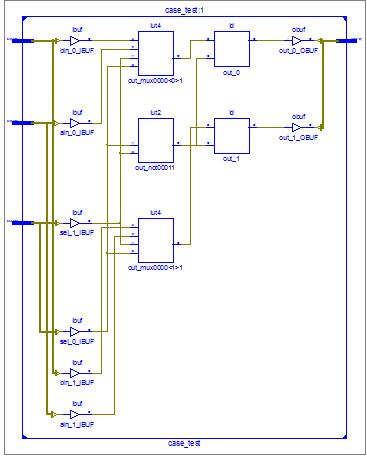

接下来我们把FULL_CASE的约束去掉再进行综合,电路图如下。

从综合后的电路图可以看出,不进行约束的比进行约束的多了几个锁存器,为什么呢?

FULL_CASE约束就是让编译器默认为case语句为完全case,所有的状态均已存在。而如果不进行FULL_CASE约束则将所有的状态都会考虑,即使有些状态不会出现,若状态不全则会产生锁存器。此项综合约束常用于状态机编程,状态机的状态有限,表示状态机状态的信号不是每个值都会出现,故用此约束可以避免锁存器的产生。有些时候即使进行FULL_CASE约束也会产生锁存器,比如:

always @(sel or ain or bin or cin)

begin

(* FULL_CASE *) case(sel)

2'b01: begin out1 =ain; out2 =bin; end

2'b10: begin out1 =bin; end

2'b11: begin out1 =cin; out2 =cin; end

endcase

end

这种情况下,有关out2部分也会产生锁存器。

接下来我们再说说PARALLEL_CASE,、该pritimive与case 语句一起使用,在综合时编译器强制生成一个并行的多路选择结构而不是一个优先译码结构,也就是我们所说的并行case。

2.运用引导语句进行case语句的约束

Synopsys提供了引导语句,利用这些引导语句同样可以达到对case的约束。下面的例子给出了几个引导语句的用法。举例1:

input [1:0] sel,ain,bin;

output [1:0] out;

reg [1:0] out;

always @(sel or ain or bin)begin

case(sel) // synopsysfull_case

2'b01: out = ain;

2'b10: out = bin;

endcase

end

从上面的例子来是,引导语句是不是特像注释啊,但是他们对DC有引导作用,并不是普通的注释。Case的引导语句主要有parallel_case 和full_case两个引导格式,他们的作用和FULL_CASE, PARALLEL_CASE是一样的。

/5

/5

文章评论(0条评论)

登录后参与讨论