10.3 if和case之间的转换

if和case语句都是条件语句,在很多情况下,能用case语句描述,也可以用if语句描述,它们之间可以转换的。比如:

我们描述的模块的功能:

输入信号:sel,clk,rst。

当sel=3’b001时,out=3’b111;当sel=3’b010时,out=3’b101;当sel=3’b100时,out=3’b011;其他的时候,out=0。

用case语句来描述:

module test_case(

input clk,

input rst,

input [2:0] sel,

output reg [2:0]out

);

always @(posedgeclk or posedgerst)begin

if(rst)

out<=0;

else

case(sel)

3'b001:out<=3'b111;

3'b010:out<=3'b101;

3'b100:out<=3'b011;

default:out<=0;

endcase

end

endmodule

用if语句描述:

module test_if(

input clk,

input rst,

input [2:0] sel,

output reg [2:0]out

);

always @(posedgeclk or posedgerst)begin

if(rst)

out<=0;

else if (sel==3'b001)

out<=3'b111;

else if (sel==3'b010)

out<=3'b101;

else if (sel==3'b100)

out<=3'b011;

else out<=0;

end

endmodule

从程序上来看,if_else结构基于优先权结构,而case为并行结构,虽然有所不同,但他们可以实现同样的模块功能,是可以相互转化的。

10.4 if和case千万别下定论

在有些情况下,可以用if_else结构描述,也可以用case结构描述,可能人问,那种条件语句会好一些呢?可能会有人说,case是并行结构,而if_else是基于优先权结构的,肯定是并行结构的case语句好啊。真的是这样的么?我们就拿上面的例子为例。

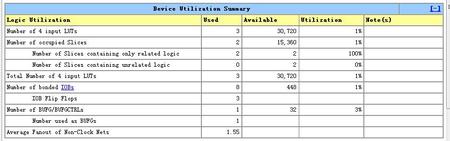

if_else结构综合布线后用过的资源情况(ISE 13.4编译器):

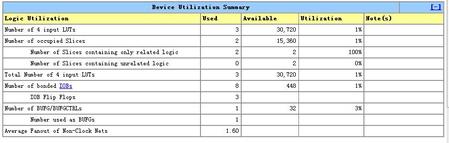

case结构综合布线后用过的资源情况:

从上面资源使用情况对比来看,资源情况是一样的,只是平均扇出有所差别。

我们再从RTL级电路来对比分析。

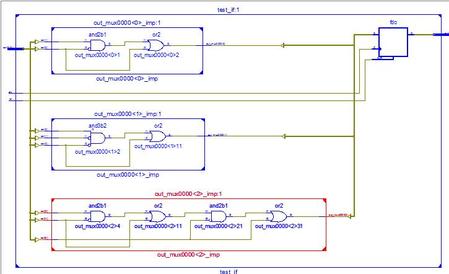

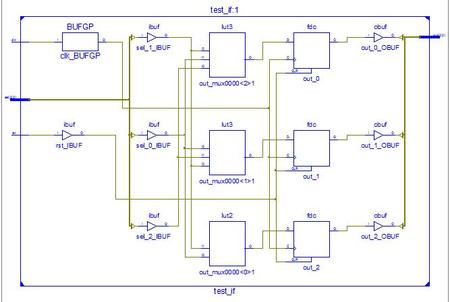

If_else结构的RTL级电路

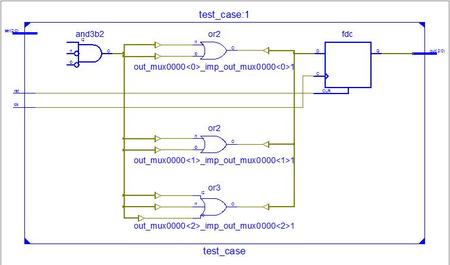

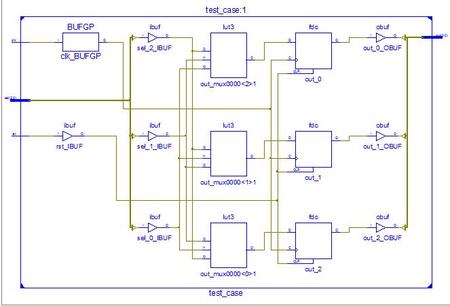

case结构的RTL级电路

从上图if_case是基于优先权结构的,而case是并行结构的,从RTL级电路来看if_else电路比case电路来说比较复杂。

接下来我们再看看Technology 电路图

if_else结构的Technology 电路图

if_else结构的Technology 电路图

从上面对比来看,两个综合出来的Technology 电路图一模一样。虽然RTL视图不一样,但从Technology 电路图和资源的消耗情况来看,很难说if和case语句那个好那个坏。而RTL视图到Technology 电路图其实也还是有差距的,他们之间的映射还是有优化的。总之,if_else和case语句实现的结构到底是怎样还是要具体问题具体分析。不能片面的强调if_else和case语句谁好谁坏。

10.5不完全的if和case

什么是不完全的if和case语句呢?就是所有可能的状态(或者条件)没有全部给出的if或者case语句。

那么不完全的if或者case语句会综合成什么样的电路呢?

还是看例子吧。

Input [1:0] ain;

input [1:0] bin;

output [1:0] cout;

reg [1:0] cout;

always @(ain or bin)

begin

if(ain>=bin) cout<=bin;

end

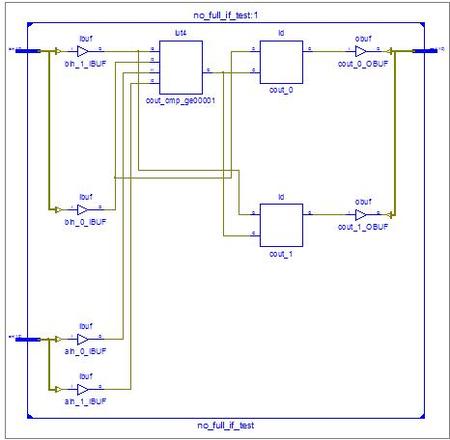

综合以后的电路图如下:

从图上可以看出,不完全的if语句会生成锁存器,不完全的case语句也会生成锁存器。

比如:

always @(sel or ain or bin or cin)

begin

case(sel)

2'b01: out = ain;

2'b10: out = bin;

endcase

end

将上面的程序综合以后同样会生成锁存器。

不完全的if(case)语句都是没带else(default)的if(case)语句,但是不带default的case语句不一定是不完全的case语句,只要用常量表达式把控制表达式的情况全部考虑到,就是完全case语句。

比如:

input [1:0] sel;

output [1:0] out;

reg [1:0] out;

always @(sel)begin

case(sel)

2'b00:out=1;

2'b01:out=2;

2'b10:out=2;

2'b11:out=3;

endcase

end

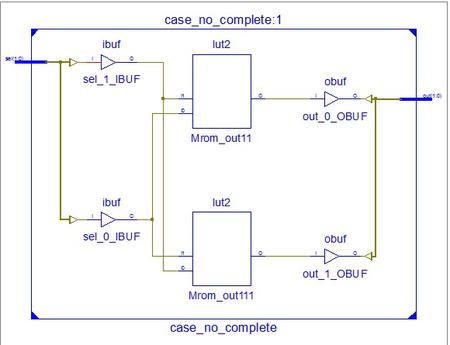

综合后的电路图如下:

从综合出来的电路图可以看出,它没有综合出锁存器,是full case语句。

很多时候锁存器不需要的,如何避免这样的锁存器的错误呢,从上面的介绍可以知道,把不完全的if和case变成完全的if和case,最常见的一种情况就是if带上else项和case带上default项。

/5

/5

文章评论(0条评论)

登录后参与讨论