看过一篇文章,讲的是一道FPGA面试题,http://blog.chinaaet.com/detail/33877.html

问题:如何用32bit的加法器和逻辑门实现2个并行的16bit加法器功能 ?

放下问题不说,先说说 加法器基本的设计方法: 串行进位加法器,超前进位加法器,模加法器等等。常用的,也是最简单的是 串行进位加法器,其组合电路如下图所示:

注意:这是一个组合电路,小方块不是触发器。这是串行进位加法器或者叫逐位进位加法器 !

用quartus综合出来的加法器,就是这种方式的加法器!

42bit 加法器,直接相加

module top(clk,rst_n,data1,data2,data3);

input [41:0]data1;

input [41:0]data2;

output reg [42:0] data3;

input clk;

input rst_n;

reg [41:0]a;

reg [41:0]b;

always@(posedge clk or negedge rst_n )

if(!rst_n)

begin a<=52'd0;b<=42'd0; end

else begin a<=data1;b<=data2; end

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin data3<=43'd0; end

else data3<=a+b;

endmodule

RTL视图:

Technology Map Viewer(局部)

可以看到把上边原理图,输入端A0-A3,B0-B3和输出端S0-S3,Co3 接上触发器,就是quartus综合后的加法器。

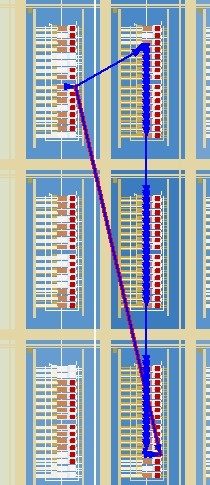

从Chip planner看,黄色LUT 实现每一位的全加器功能(原理图的FA),红色是输出寄存器,箭头表示连接,向下的箭头是进位线。

串行进位加法器,最大的缺点: 每一位的相加必须等低一位的进位产生以后,才能进行,如果位宽比较大,这种组合逻辑延时势必会影响到Fmax,加法器的速率不会太高 !

以上边42bit加法器程序为例,b[0]到b[41]是源同步,中间经过40个全加器LUT,如下图

上边的42bit加法器,最高速率为 183MHZ

那么怎么提高加法器时钟速率呢 ??流水线 ,下一篇博文继续。。。。。

/1

/1

文章评论(0条评论)

登录后参与讨论