1、 ddr/ddr2控制器(包括数据路径)都是自己写的,纯手工打造,纯logic,不用任何IP,也不考虑某些器件专门的存储器接口,比如IOE中DQ,DQS专用管脚等。

2、不同系列FPGA,不同版本Quartus,Altera给出了不同的ddr控制器IP及实现方式。

QuartusàMegaWizard Plug-In ManageràInterface-àExternal Memory

IP

主要三类: ddr / ddr2 SDRAM Controller

ddr / ddr2 SDRAM High-Performance Controller (II)

ddr / ddr2 SDRAM Controllers with ALTMEMPHY IP

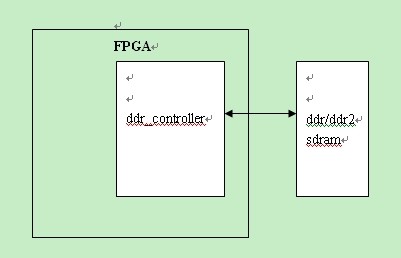

ddr / ddr2 SDRAM Controller 是比较早的方式,Cyclone Cyclone II Stratix 等使用的此IP,

这一个Megacore IP 同时含有了 Control logic 和 Data path 。

用此IP生成的ddr sdram controller 中包括了 control logic(给ddr 各种命令) 和data path(读写数据,双倍速率控制,DQS延时移相等)。

data path 模块使用了关于IO 的megafunction

一些系列的FPGA 比如Stratix ,data path 模块使用的IOE 中的 DQ ,DQS 及一些LEs ;

而Cyclone 系列data path模块使用的都是LEs

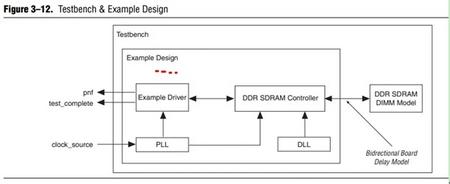

使用此IP 除了产生含有data path 的控制器外,还同时产生了 例子 Examlple 文件和 testbench文件 ,PLL ,DLL 等时钟文件,以及模拟ddr sdram模型文件,形成一个整体的仿真环境。(实际用到自己工程的只需要IP产生的控制器)

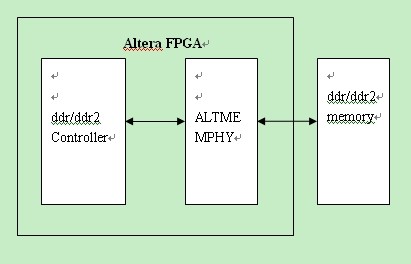

{C}ddr / ddr2 SDRAM High-Performance Controller (II) 和 ddr / ddr2 SDRAM Controllers with ALTMEMPHY IP 实现方式差不多,后者可以看作是前者的升级版,在高版本的Quartus中都是后者实现方式。下图的ddr/ddr2 Controller 就是使用这种Megacore IP,结合起来控制 ddr memory .

{C}ddr / ddr2 SDRAM High-Performance Controller (II) 和 ddr / ddr2 SDRAM Controllers with ALTMEMPHY IP 实现方式差不多,后者可以看作是前者的升级版,在高版本的Quartus中都是后者实现方式。下图的ddr/ddr2 Controller 就是使用这种Megacore IP,结合起来控制 ddr memory .

注意: 使用ddr / ddr2 SDRAM High-Performance Controller (II) 和 ddr / ddr2 SDRAM Controllers with ALTMEMPHY IP 时,除了产生ddr controller ,还会自动调用 ALTMEMPHY IP ,产生相应ALTMEMPHY例化文件,以及Example Files 。

Altera 建议:

Altera recommends that you construct all DDR2 or DDR SDRAM external memory

interfaces using the Altera ALTMEMPHY megafunction.

You can implement the controller function using the Altera DDR2 or DDR SDRAM memory controllers, third-party controllers, or a custom controller for unique application needs.

这是由于 DDR2/DDR 的数据接口部分,有双倍速率,速率变换,DQS,相移等等操作,直接写logic,比较难实现(当然可以自己写),某些系列Altera FPGA 内部 IOE 部分也做了专门的接口,使用ALTMEMPHY可以方便的调用。

Altera ddr controller 或者自己写ddr controller 或者 第三方controller , Altera 接口即ALTMEMPHY

如果,由于特性不匹配(例如:要求低延迟等),您无法使用基于 ALTMEMPHY宏功能的存储器接口,怎么办?

又如果,您必须创建一种 Altera不支持的存储器接口,例如:移动 DDR,怎么办?自己写可以,但是Altera 提供了ALTDLL 和ALTDQ_DQS 宏功能,以ALTDDIO_IN,ALTDDIO_OUT ,ALTDQ, ALTDQS ,ALTDLL等宏功能,以满足各类个性的设计。

/2

/2

用户1605975 2014-7-29 00:11

pengchengcheng082_593158939 2014-5-9 19:07

用户1605975 2014-5-8 16:58