Primace结合modelsim进行仿真设计

京微雅格的自主研发的EDA工具Primace是支持调用第三方工具modelsim进行仿真开发的,在Primace4.2版本及以后支持RTL仿真,在Primace5.0以后支持RTL仿真和后仿真。具体步骤如下:

1、安装好modelsim,并安装好license。能正常启动modelsim就可以了。

2、在primace工程选项中设置好modelsim的目录。如下图:

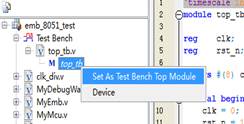

3、编写testbench文件或是把编好的testbench文件添加到工程中,并选择文件属性将其设置为testbench文件。

选中top_tb模块,设置为testbench顶层模块。

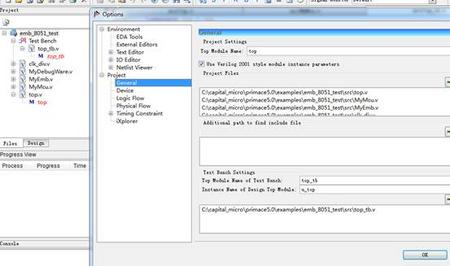

4、在工程属性的General选项页里设置testbench文件模块和例化的名称:

Top Module Name of Test Bench:testbench模块的名,激励文件模块。

Instance Name of Design Top Module:testbench模块里调用设计顶层模块的例化名

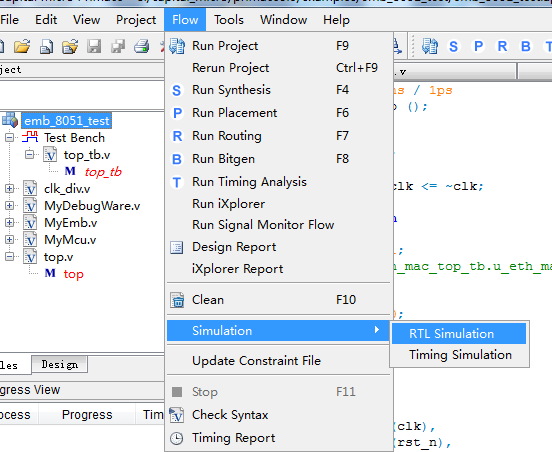

5、点击Flow->Simulation->RTL Smulation 进行功能RTL仿真。这时Primace软件会生成一个modelsim里使用的do文件并自动执行do文件。执行的过程中会把在modelsim里用到的库文件也加载到modelsim里,添加所有的源文件到modelsim里并编译等。没有错误的话就会出现待仿真状态。

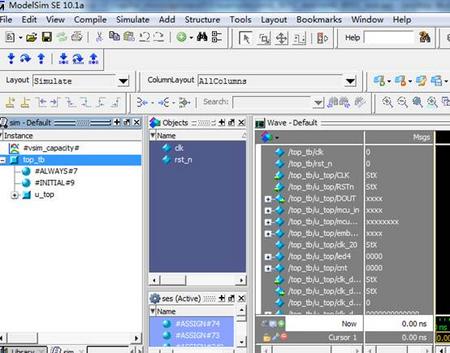

这时可以看出,modelsim已经把所有的信号都添加到wave窗口中,用户只需删减信号,留下自己关心的信号,就可以输入run 1ms,稍等就可以看到仿真波形了。

这时可以看出,modelsim已经把所有的信号都添加到wave窗口中,用户只需删减信号,留下自己关心的信号,就可以输入run 1ms,稍等就可以看到仿真波形了。

6、后仿真时,只需执行Flow->Simulation->timing Smulation 即可。

7、注意事项,在仿真过程中,如果仿真不通,请依次排除以下问题:

l Testbench里必须要有类似的 `timescale 1ns / 1ps 时间轴分辨率语句

l 在工程选项里要设置好testbench模块名和设计模块的例化名

l Modlesim的路径要填写正确,具体到win32目录。

l 在工程里,要把testbench文件设置为testbench类型。

8、脱离primace仿真

如果每次都在Primace里调用modelsim仿真比较麻烦,可以直接在modelsim里运行do文件进行仿真。在工程的目录下,会有一个simulate目录,如果执行一次RTL仿真,就会自动生成top_rtl_sim.do文件,如果执行一次timing仿真,会自动生成top_post_timing_sim.do文件。在modelsim里,把当前目录切到simulate目录下,直接运行do文件就可以仿真了。

do top_rtl_sim.do

do top_post_timing_sim.do

懂do文件的朋友,可以打开do文件分析一下,自己修改do文件也可以,随心做出自己想要的仿真批处理文件。

/4

/4

文章评论(0条评论)

登录后参与讨论