京微雅格是世界上除美国以外唯一自主研发并成功量产现场可编程逻辑(FPGA)芯片的公司,目前拥有数百项技术专利和近百款产品。目前,已经有越来越多的用户都开始使用国产FPGA来做自己的设计,然而在FPGA的开发过程中,免不了要对设计进行仿真。京微雅格的FPGA是支持在modelsim中进行仿真的。

京微雅格的FPGA需要在Primace软件中进行开发,为了便于客户进行仿真设计,在Primace5.0及以上版本都支持在工程中直接调用仿真工具Modelsim。同时,也支持在modelsim中直接进行调用京微雅格仿真库的方式脱离primace软件进行仿真。这对利用modelsim进行自动化仿真提供了极大的便利。

Capital Micro Company is the only company which independent research and have successful produce FPGA chips except the USA. Currently, there are more and more users are beginning to use national FPGA to design, but in the FPGA development process, they have to simulate the design before debug. Capital Micro’s FPGA can be simulated in modelsim.

Capital Micro Company’s FPGA needs to be developed in software named Primace. In order to facilitate customer simulation design, users can directly call Modelsim in Primace5.0. It also supports simulation in modelsim with library that Capital Micro supplys. This provides a great convenience for automated simulation.

Primace5.0及以上版本的软件,直接支持在软件中直接调用modelsim软件进行仿真。具体步骤如下:

一、下载安装Modelsim,能正常使用Modelsim。

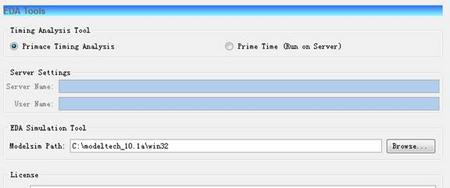

二、设置Primace软件的EDA工具路径。打开Primace软件,选择Tools菜单下的Options选项,弹出设置窗口。点击左边窗口Environment分支下的EDA Tools标签,在右边的窗口中设置好EDA Simulation Tool下的Modelsim Path路径,例如“C:\modeltech_10.1a\win32”,需要具体到win32目录,如下图所示。

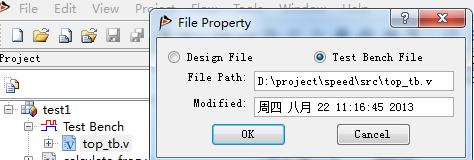

三、编写testbench文件并将文件添加到工程中。并设置文件属性为testbench。

该testbench文件是仿真激励文件,只有添加到工程中,并且设为testbench属性后,才能让Primace软件识别为激励文件,才能正常启动仿真过程。下图所示为添加名为top_tb.v的testbench文件。

经过这步,工程里就具备了所有的条件,既有源码Design File,也有Test Bench File。

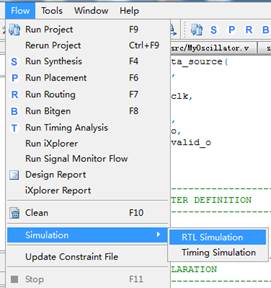

四、运行菜单Flow->Simulation->RTL Simulation 启动RTL级的前仿真。这时Primace会自动调用Modelsim软件,并把所有源码在Modelsim里编译,并自动启动仿真窗口。

同样,运行Flow->Simulation->Timing Simulation可以启动包含时延信息的后仿真,得到的波形是经过布局布线后在芯片内的真实波形仿真结果。

primace调用modelsim后,在modelsim的脚本窗口会发现一些信息,经过查看信息就大概能了解整体仿真的过程是如何进行的。这种仿真,实际是Primace软件启动modelsim后,执行了do文件的结果。

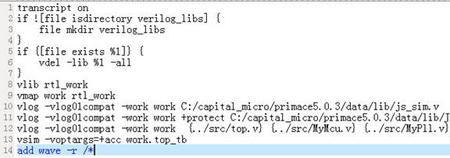

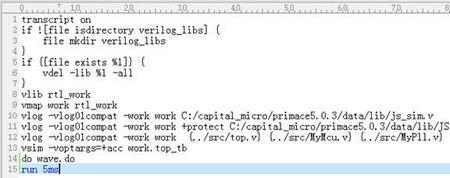

执行过一次RTL Simulation之后,Primace会在工程目录下新建simulate目录,并自动生成所有相关的仿真文件,包括扩展名为.do的文件。用文本工具打开*.do文件可以看到其内容:

Modelsim的do文件是modelsim支持的一种批处理文件:

第8行:建立rtl_work库

第9行:把work库映射到rtl_work库上来

第10行:编译京微雅格的FPGA仿真库文件

第11行:编译工程里使用到的IP仿真核库文件

第12行:编译工程里的源文件,激励文件

第13行:启动modelsim仿真

第14行:添加所有信号到波形文件中

当Modelsim执行到此时,用户只需要执行相应的时间就可以进行仿真了。

在用Primace调用Moldesim进行仿真时,如果需要更改代码重新编译仿真,每次都去点击Flow->Simulation->RTL Simulation进行仿真,会比较麻烦。其实在连续改代码并生新仿真的过程中,可以按以下步骤进行:

1、 工程第一次可以运行Flow->Simulation->Timing Simulation过程,让软件自动建立do文件,并调用modelsim仿真之后,不要再关闭modelsim程序,直接在modelsim里的脚本执行窗口执行do 文件就可以启动仿真:如输入 do top_rtl_sim.do 并按回车确认。

2、 仿真过程不要关闭modelsim,修改源代码时,可以用modelsim文本编辑器,也可以使用UE等第三方文本编辑器,修改后在脚本执行窗口直接运行do文件。

3、 为防止每次都手动修改并添加仿真信号,可以保存需要的仿真信号。在Modelsim程序的File菜单下,点击Save Format,保存信号文件为wave.do文件。

要自动添加这些信号,修改第14行为 “do wave.do”。如果再想自动执行一段时间,可以在15行添加 “run 5ms”,这样仿真停止后就可以直接观察所需要的信号了,如下图所示:

能不能不用Primace软件调用modelsim的方法,直接在Modelsim里仿真呢?答案是肯定的。这需要有京微雅格的仿真库文件,一旦有了仿真库文件,就可以在第三方仿真工具中灵活进行仿真。具体过程如下:

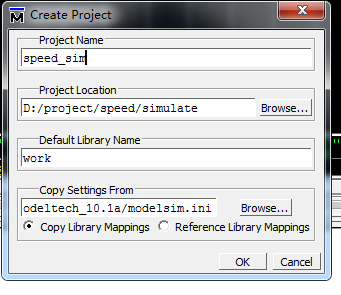

1、 建立modelsim工程,工程名:speed_sim

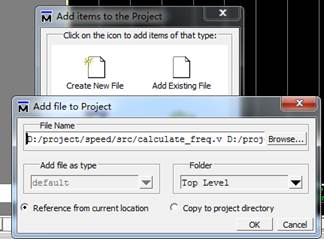

添加源文件及testbench文件:

2、 添加仿真基础库文件到工程里来

仿真库文件在安装primace的目录里:C:/capital_micro/primace5.0.3/data/lib/

3、 添加IPcore必要的源文件。例如工程里使用到FIFO,就到工程目录下的ip_core目录下找相应的源文件,也添加到工程里来。

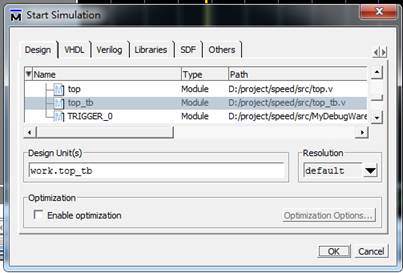

4、 编译整个工程,把必要的语法错误改掉,直到没有错误。启动仿真

使用中的简单方便的技巧:

1、 在波形文件中添加的信号,可以存为wave.do文件,需要的时候执行do wave.do就可以把所需的信号添加到波形窗口中。

2、 更新过原代码后,不需要重新启动仿真,只需要编译一下更新的源代码文件,然后点击复位按钮,把仿真器的所有状态复位,再执行设计的时间,就是新的更新后的代码仿真波形了。这样可以不用每次都通过start simulation启动仿真。

/4

/4

用户377235 2015-10-18 01:55