基于FPGA的数字滤波设计—FIR设计3

.3 FIR滤波器总结

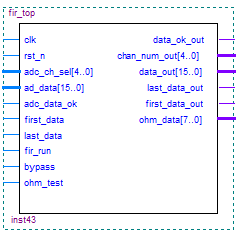

按照上述设计最终生成的原理图顶层如图3.9所示。我们可以计算出FIR滤波所花费的时间。

首先介绍adc_ctrl模块和fir模块之间的关系。

adc_ctrl模块:

输出信号data_ok、first、last信号,高电平有效,并且持续1个clk_adc(3M)时间。通道选择adc_ch_sel和数据输出adc_ad_out端口在data_ok等信号有效之前已经准备好,并且注意,adc_ch_sel在data_ok有效时输出1-12 Or2-24。同时保证在CS拉低后的6个clk_adc后改变通道值。

fir模块:

在run上升沿发起后,等待ram中存满1536个新数据后,检测到adc_ctrl模块输出的data_ok信号的下降沿后(保证数据完成保存后)开始计算当前通道,当前data_ok信号指定的输入数据的fir值。大约需要不大于70个sys_clk时钟周期计算结果。Fir模块需要的chan_sel信号是0-11 or 0-24,所以由adc_ctrl模块送过来的adc_ch_sel需做调整。

时序对接要求:

假设:sys_clk=100M 10ns

adc_clk=6M 166ns 超频

clk_sample=10k 100us 超采

采集时间计算:

adc_ctrl模块需要23个adc_clk时钟周期输出一个采集数据,按照最大通道数24计算,一个采样周期clk_sample,采集需要的时间为:166ns*23*24=91632ns=91.6us<100us, 即需要大约9163个sys_clk周期。那么按照8K超采,adc_clk最低需要多高的时钟?经计算需要adc_clk>4.3M。注意此时间并不包括组帧等其他时间。

FIR运算时间计算:

计算一个数据的64阶fir值,需要不大于70个sys_clk周期。同时,FIR是在每个data_ok信号的下降沿后开始计算的,那么必须在下一次data_ok信号的下降沿来之前计算完成。知道两个data_ok有效信号之间的间隔为23个adc_clk周期。那么必须满足:

70sys_clk<23 adc_clk

如果30M的sys_clk,3M的adc_clk,那么可以计算出,FIR最大阶数在200以上。

从以上结论可以看出,利用FPGA设计FIR数字滤波器的瓶颈并不在于FPGA运算速度不够快,而是在计算72个通道FIR时需要保存很多的历史数据,对FPGA内部的存储器提出了更大的要求。那么我们知道,64阶FIR并不能完成来时提出的指标要求,必须寻求其它更加可行的方案。

/5

/5

文章评论(0条评论)

登录后参与讨论