原文网址:http://wenku.baidu.com/link?url=s6vfSUEYn654_R3Btr4nFXSvjxsq1MGmhUcWmmmHRO7TexJBOSkPK59wF26cER6LVM2uz2SRwO32IviDFngvn4K9qd8PCyOYDlJmeY8LQMi

♦Local Bus总线的读写时序

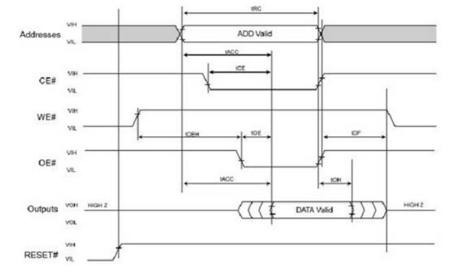

下图为FLASH器件MX29LV002CBTI的读时序,该FLASH器件提供的Local Bus接口,Addresses信号是从Local BUS地址信号(已经解复用了),Outputs是Local bus的数据信号。在第一个时钟周期内,Address信号线上传输的是目标器件的地址信号,此时CS#、OE#、WE#都处于高电平无效状态,并且Outputs输出的数据无效。在第二个时钟周期内,CE#变为低电平,表示目标器件已经被选中,接着OE#也变为低电平(大多数情况下,CS#和OE#几乎是同时有效的),表示开始进行读操作,主控制器在CE#和OE#都为低电平有效的时候对Outputs上的数据进行采样(通常做一定的延时后再采样,以保证采样数据的正确性),采样到的数据即为要读取的数据。WE#和OE#不会同时变低的,因为Local Bus总线是半双工工作方式,不可能同时进行读写两种操作。(点开看清楚大图)

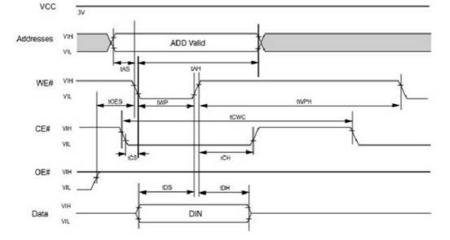

下图为FLASH器件MX29LV002CBTI的写时序,在WE#和CS#同时为低有效的情况下,Flash器件从数据总线上采样数据,然后写到指定的地址空间里去。对比下这两个图,我们会发现,读操作时,OE#信号差不多在ADD Valid周期的中间部分有效,而写操作时,WE#信号几乎在ADD Valid周期的开始部分有效,为什么有这个差异呢?其实想想也不难,因为读操作流程是:总线控制器给目标器件发读取数据指令,等目标器件收到指令后再将总线控制器要读取的数据传回来,这中间有线路的延时及目标器件的延时。而写操作则不然,可以将写操作命令和要写的数据同时传到目标器件那边去,几乎没什么延时。

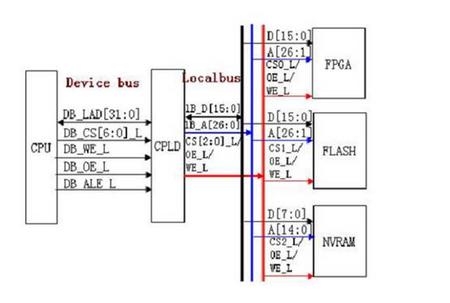

♦Local Bus总线的典型应用如下图所示:

如上图所示,CPLD对Device bus总线进行了解复用后连接到FPGA、FLASH和NVRAM(CPLD可以对Local Bus总线的大小端模式进行切换),利用CS0_L、CS1_L和CS2_L三根片选信号线来区分Local bus总线上的三个器件。FPGA使用了32根数据线中的16根,32根地址线中的26根。

我们再仔细看一下其地址线标号,为A[26:1],我们也许会疑问,会不会是搞错了啊,怎么不是从最低位地址AO开始啊?是的,我没有写错,你也没有看错,实际上就是从A1开始的。这是因为当数据线宽度为16位双字节模式(也叫WORD模式,四个字节叫DWORD模式,单字节叫BYTE模式)时,Local bus总线的A1变为地址的最低位(A0悬空不用),用它去连接器件的最低位地址线A0。

这其实也很好理解,因为对于同样大的存储空间来说(我们可以将存储空间想象纵横交错的棋盘状),当数据线D(棋盘中的横线)增加一倍的情况下(从8位增加到16位),要想保持数据线和地址线的乘积不变(存储空间容量不变),那么就要将地址线减少一半(对于译码前的数据线来说,就是减少一根线)。下面的NVRAM用的是8位BYTE模式,所以最低位地址仍然用A0去接。

/5

/5

文章评论(0条评论)

登录后参与讨论