原文网址:

http://wenku.baidu.com/link?url=s6vfSUEYn654_R3Btr4nFXSvjxsq1MGmhUcWmmmHRO7TexJBOSkPK59wF26cER6LVM2uz2SRwO32IviDFngvn4K9qd8PCyOYDlJmeY8LQMi

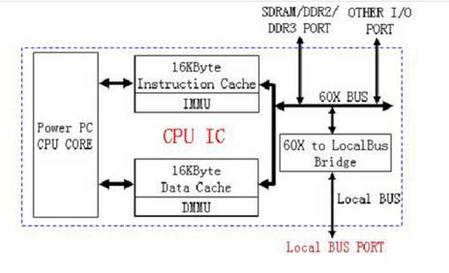

Local Bus总线又称为CPU总线,根据高低位地址线序的差异,又可分为Motorola CPU总线和Intel CPU总线。古老的CS51单片机就是Intel CPU总线的典型代表,而我们常用的Power PC就是Motorola CPU总线架构,它是从60X总线衍变过来的(60X总线支持64、32、16、8四种可选位宽模式),由于Local Bus总线是直接从60X总线上通过桥片分出来的,所以它和60X总线是同步同频的,进行数据数据读写时与60X总线共享带宽,不需要内核提供额外的处理。如下图所示:

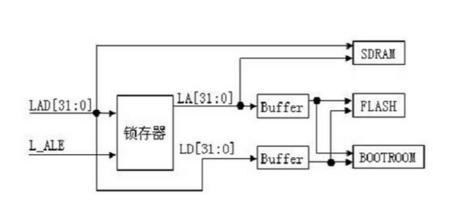

Device Bus(数据/地址复用总线解复用后的Device Bus叫Local Bus)总线一般采用数据/地址线复用的形式,通常为32位宽,使用时需要将总线的数据和地址分离出来再分别接到目标器件的数据和地址端口,如连接到低速设备时还需要通过Buffer起来来进行驱动和隔离。在早期的设计中,通过用信号锁存器来分离总线中的数据和地址(如经典锁存器SN74LVC16373),不过现在基本上都是通过逻辑器件CPLD来进行解复用的。利用锁存器373对Device Bus总线数据/地址解复用原理如下图所示。

在上图中,L_ALE是地址锁存信号,低电平有效,当L_ALE出现一个低电平脉冲时,锁存器的输入端口对LAD[31:0]信号进行采样、锁存并从输出端口输出,直到下一个L_ALE低电平脉冲到来时,其输出状态才发生改变,Device Bus总线在输出地址信号时将L_ALE信号驱动为低电平,输出数据信号时,将L_ALE驱动为高电平,锁存器正式利用这个特点轻松实现Device Bus总线上数据和地址的分离。

Local Bus总线上的数据读写分为同步模式和异步模式。在同步模式下,需要一个外部时钟信号供接收端和发送端共用,利用时钟信号的上升沿对数据进行采样,SDRAM、SSRAM等高速信号使用同步模式;异步传输模式下,不使用时钟信号对数据进行采样(芯片内部还是需要有系统参考时钟来产生时序的),而是利用片选信号CS、写使能信号WE和读使能信号OE对数据进行采样,使用异步模式的器件有FLASH、BOOTROM等。

♦Device Bus总线数据及控制信号列表及功能说明:

1).LAD[31:0]:数据/地址复用信号,数据线宽度可设为8、16、32为三种模式;地址线根数可根据实际存储空间大小来选取,比如,16根地址线可支持的寻址空间大小为(针对8位宽存储器件,16位宽存储器件需要乘以2,其他类推):216=65536Byte=64KByte。做为地址线时是单向输出,三态总线,LVTTL电平。做为数据线时是输入/输出双向信号,三态LVTTL。

2).CS_L:Chip Select,器件片选信号,低电平信号,Local Bus总线上每个器件都有一个独立的CS_L信号,某个器件上的CS_L信号为低电平时表示这个器件被选中,Local Bus总线主控制器可以对其进行读写操作;

3).WE_L:Write Enable,写使能信号,低电平有效,Local Bus总线上的WE_L信号为低电平时,表示在进行写操作,在异步传输模式下,它与CS_L信号配合对写数据进行采样;

4).OE_L:Output Enable,读使能信号,跟WE_L类似,在异步传输模式下与CS_L信号配合对读数据进行采样;

5).ALE_L:地址锁存信号,低有效,其功能已经在前面介绍过了,不在赘述;

6).Rdv:应答信号,对读写操作进行应答;

7).INT:中断输入信号;

8).RST_L:复位信号;

9).CLK:参考时钟信号,只在同步传输模式下使用,异步模式下不使用,设计中将其悬空即可。

实际应用中,一般只使用LDA/CS_L/WE_L/OE_L/ALE_L这些信号,其他信号作为选用。

上面介绍的是针对Intel CPU总线的,Motorola CPU总线有一点点差异,后者将OE_L和WE_L合并成一根控制信号,称为R/~W,当其为高电平时表示“读”操作,为低电平时表示“写”操作。另外,后者还有一个DS控制信号,当其为低电平时表示总线上传输的数据是有效的,否则为无效。

如果Local Bus总线上挂SDRAM等高速存器器件时还需要行列选择信号RAS和CAS以及数据奇偶校验信号DP。

♦CPU总线的大端模式和小端模式

Intel系列的CPU总线是小端模式,也叫Little-endian byte ordering,其特点是低有效字节在低地址位,高有效字节在高地址位。

Motorola CPU及Power PC架构总线是大端模式,也叫Big-endian byte ordering,其特点是低有效字节在高地址位,高有效字节在低地址位。

所以在使用大端模式总线连接外部器件时需要将地址线进行倒序,即最高位地址线与外部器件的最低地址位相连,最低地址位地址线与外部器件的最高地址位相连,其他依次连接。

/5

/5

文章评论(0条评论)

登录后参与讨论