看完了软件的安装,接下来我们就来了解些硬件及设计注意事项。

2 硬件设计

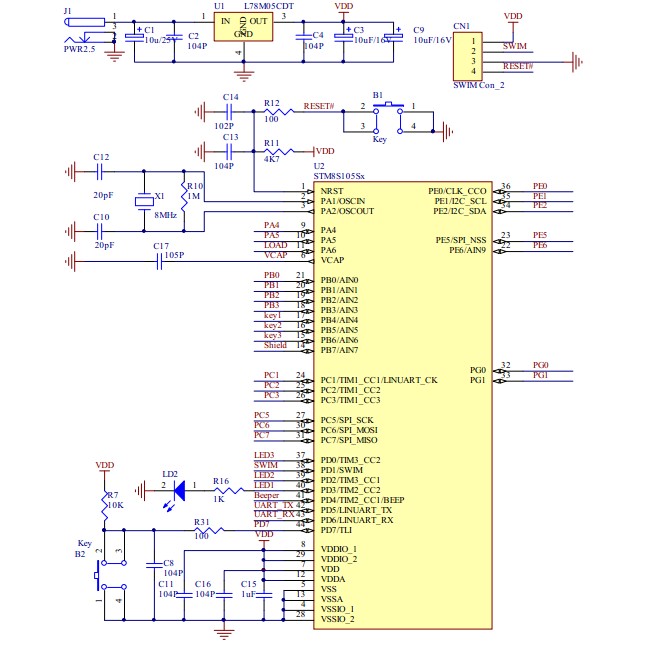

下面的原理图利用STM8 MCU (以STM8S105S4-PKT评估板为例)。本节将通过这个原理图向大家介绍如何开始STM8 的硬件开发,以及需要注意的地方。

2.1 电源

STM8S系列单片机的工作电压约为2.95V ~ 5.5V(具体的电压以Datasheet提供的数据为

准)。因此在设计时要注意保证MCU的供电电源在这个范围之内。

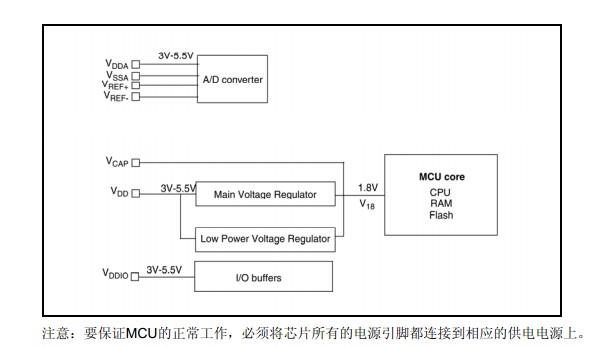

对于不同封装的STM8S MCU ,最多会有下面这些电源引脚:

● VDD/VSS: 主电源 (3 V to 5.5 V)

● VDDIO/VSSIO: I/O 口供电电源 (3 V to 5.5 V)

● VDDA/VSSA: 模拟电路的供电电源

● VREF+/VREF-: AD 转换模块的参考电压

每对VDD,VSS只见都必须加去耦电容。若VDD,VDDIO,VDDA 是相邻的,则可供用一个去耦电容。例如,上面原理图中的引脚7和引脚8可以供用一个去耦电容。

在部分封装的MCU上,可能会有Vref+和Vref-引脚。这两个引脚的输入电压是ADC模块的参考电压。在没有这两个引脚的MCU上,这两个引脚是在MCU内部直接连接到VDDA 和VSSA 上。如果有外部电路提供参考电压,需要注意Vref+和Vref-的电压必须在VDDA 和VSSA 的范围内,

例如:对于STM8S207 来说:

2.75V < Vref+ < VDDA

VSSA < Vref- < 0.5V

2.2 Vcap

Vcap引脚是STM8S系列MCU内核供电电源的引出脚。为了保证内核能够正常运行,必须在Vcap引脚加去耦电容,并且要求距离MCU越近越好。在参考手册上,对这个去耦电容的要求是470nf,考虑到有些电容的偏差比较大,我们建议这个引脚上的电容取680nf~1uF 比较合适。注意不能使用电解电容,其较差的高频特性不适合用于此处。

2.3 复位电路

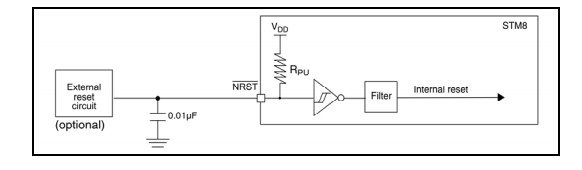

STM8S的复位引脚NRST 是一个输入/ 开漏输出的双向引脚,内部有一个约30~60k左右的弱上拉。 NRST 引脚上最小500ns 的低电平就会使MCU产生复位。同时NRST 引脚也可利用开漏输出来使其他外部设备产生复位。

不管是什么原因引起的MCU复位都会在NRST引脚产生最少20us的低电平。

一般来说,复位电路可采用传统的外部RC方式,如上面的原理图所示。另外,由于MCU本身有内部弱上拉,因此外部的上拉电阻也可以不加。下图是数据手册提供的推荐电路。

2.4 时钟

STM8 可使用外时钟或内时钟,当使用外时钟时,如果MCU主频超过16MHz,要在选项字节中配置等待周期为1 。STM8 的内时钟为16MHz,可根据需要进一步分频。其内部有3或4位的频率微调器,经过校正后其频率误差理论上可不大于0.5%( 频率微调器为3 位) 或0.25%(频率微调器为4位)。

2.5 I/O 口的分配

1. 要注意选项字节的配置,尤其注意I/O 重映射功能状态是否与实际项目相符合

2. STM8的I2C 接口为真正的开漏接口,意味着其没有内部上拉电阻和对电源的保护二极管。

3. 并非所有的I/O 口都是大电流口,当需要I/O 有很强驱动能力时要检查其是否需要外加驱动。

4. SWIM接口要保证上电时为稳定电平以防止MCU误进入调试模式。

上面只是设计电路的一些非常重要的注意点,关于更详细的电路设计及EMC……还得参考ST的参考手册,其中有更精彩的论述。

/4

/4

文章评论(0条评论)

登录后参与讨论