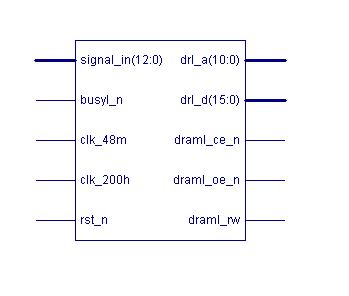

FPGA脉冲采集模块设计<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

最近组长给分配的任务,这几天一直在做,比较郁闷的是用的器件是XC400XL系列的,只有ISE4.1支持,用惯了7.1i的我还是要适应一阵子(关键4.1是一个试用版的)。挺折腾的,不说了,放上顶层模块:

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: wuhouhang

//

// Create Date: 12:39:17 07/24/01

// Design Name:

// Module Name: top_dram

// Project Name:

// Target Device:

// Tool versions:

// Description: 每隔5ms把累加的13路脉冲值写入双口RAM(IDT7133)中

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module top_dram(clk_48m,clk_200h,rst_n,busyl_n,signal_in,draml_rw,draml_ce_n,draml_oe_n,drl_d,drl_a);

input clk_48m; //主时钟信号48MHz

input clk_200h; //5ms方波(与13路信号同步)

input rst_n; //复位信号,低电平有效

input busyl_n; //双口RAM左边忙标志,低电平有效

input[12:0] signal_in; //输入的13路信号

output draml_rw; //双口RAM的左边读/写控制端口:高电平--读,低电平--写

output draml_ce_n; //双口RAM的左边芯片使能端口,低电平有效

output draml_oe_n; //双口RAM的左边输出使能端口,低电平有效

output[15:0] drl_d; //双口RAM的左边16bit数据总线

output[10:0] drl_a; //双口RAM的左边11bit地址总线

//wire clk_200h; //200Hz(5ms)时钟分频信号

wire clk_12m; //12MHz时钟分频信号

wire[15:0] sig_reg0,sig_reg1,sig_reg2,sig_reg3,sig_reg4,sig_reg5,sig_reg6,sig_reg7,

sig_reg8,sig_reg9,sig_reg10,sig_reg11,sig_reg12; //13路输入信号脉冲计数寄存器

//时钟分频模块

clock_div clock_div( .clk_48m(clk_48m),

.rst_n(rst_n),

.clk_12m(clk_12m));

//锁存13路输入数据模块

count count( .clk(clk_48m),

.clk_200h(clk_200h),

.rst_n(rst_n),

.signal_in(signal_in),

.sig_reg0(sig_reg0),

.sig_reg1(sig_reg1),

.sig_reg2(sig_reg2),

.sig_reg3(sig_reg3),

.sig_reg4(sig_reg4),

.sig_reg5(sig_reg5),

.sig_reg6(sig_reg6),

.sig_reg7(sig_reg7),

.sig_reg8(sig_reg8),

.sig_reg9(sig_reg9),

.sig_reg10(sig_reg10),

.sig_reg11(sig_reg11),

.sig_reg12(sig_reg12));

//数据写入双口RAM模块

dualram dualram( .clk(clk_12m), //

.rst_n(rst_n),

.clk_200h(clk_200h),

.busyl_n(busyl_n),

.sig_reg0(sig_reg0),

.sig_reg1(sig_reg1),

.sig_reg2(sig_reg2),

.sig_reg3(sig_reg3),

.sig_reg4(sig_reg4),

.sig_reg5(sig_reg5),

.sig_reg6(sig_reg6),

.sig_reg7(sig_reg7),

.sig_reg8(sig_reg8),

.sig_reg9(sig_reg9),

.sig_reg10(sig_reg10),

.sig_reg11(sig_reg11),

.sig_reg12(sig_reg12),

.draml_rw(draml_rw),

.draml_ce_n(draml_ce_n),

.draml_oe_n(draml_oe_n),

.drl_d(drl_d),

.drl_a(drl_a));

endmodule

综合后的RTL视图:

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

一共三个模块一目了然:

仿真的视图:

用户619565 2014-3-7 01:19

578645627_583309889 2011-8-8 12:32

用户1678515 2011-8-7 14:08

用户1620464 2011-7-30 00:39

用户242716 2010-10-4 15:52

用户1373959 2010-8-25 17:07