DMA无处不在

在一次闲聊中,一位朋友就问其中几位物流专业的同学“你们是什么专业的”。答曰“物流”。那位朋友就调侃说“物流就是把东西搬来搬去”。同学不服,纠正说“应该是‘实现物体空间的位移‘”。然后我就问自己,“我们这般电子工程师在干什么?很多时候(当然不完全是)不也是在做物流吗?只不过对象不同而已,因为我们是‘实现数据(信息)的空间位移’”。哈哈,说得通俗一点,“通信”不也是“物流”吗?

言归正传,数据的传输可以通过各种各样的途径,载体可以是模拟的,也可以是数字的;协议可以五花八门的,位宽也可以或大或小,速度当然也是各有千秋,电平不同,稳定性也有差异……而这里要提一种在CPU系统数据传输中很常见的通信方式——DMA(Direct Memory Access),即直接存储存取。在很多较高端的DSP或是MCU中,都存在着这样一种数据传输功能,引一段网络上常见的对DAM的解释如下。

DMA是一种不经过CPU而直接从内存存取数据的数据交换模式。在DMA模式下,CPU只须向DMA控制器下达指令,让DMA控制器来处理数据的传送,数据传送完毕再把信息反馈给CPU,这样就很大程度上减轻了CPU资源占有率,可以大大节省系统资源。<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

那么也就是说,DMA工作时可以和正常工作的CPU毫不相关,CPU可以控制(或者确切的说是配置)DMA,而DMA和CPU和并行工作。大家都明白CPU工作大多要有软件程序运行,而软件的顺序决定了它的速度和性能是有瓶颈的,但是一旦有了DMA这个功能,就能够给系统带来一定性能上的提升。打个不恰当的比方,还是和前面提到的物流相关,在A和B地之间原本只有一条铁轨(对应一条总线)一列火车(对应一个CPU)进行运输,那么如果要在一个月或一年之内多运一些东西(加大数据吞吐量),除了加快火车速度外别无选择,但是DMA就相当于在火车运转过程中的空闲路段上(不被总线占用的模块)增加了一列火车,他不负责全程运输,他只负责一个路段的运输(局部数据传输),并且只能在主运火车不占用该路段的情况下工作(由总线仲裁器进行判断)。

换句话说,DMA可以提升系统的数据吞吐量。因为DMA能够传送CPU配置好的初始地址到目的地址之间的数据,他在初始化并启动之后不需要CPU程序的任何其他控制,直到传输结束递交一个中断信号。DMA的吞吐量很大程度上决定于与他所连接的模块(可以是存储器、总线、芯片等等)。当然,越多的DMA通道也就越能够加大系统的数据吞吐量。就如图1所示。从一个DMA到两个DMA,可以在系统运行中,让每个模块都不处于闲置状态。

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

图1

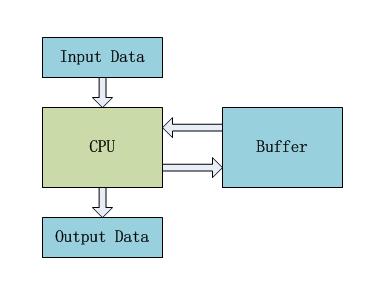

举一个很简单的CPU系统中使用DMA的例子。如图2所示,在不是用DMA的CPU系统中,需要完成一个数据采集(输入)、数据处理、数据传输(输出)的功能,就需要CPU从始至终不停的运转,这三个步骤都是CPU的程序来控制,采集到数据,然后扔进buffer(通常是存储器),处理的时候也需要从buffer里取数据,处理完成还要送出去。同样的功能,如图3所示的含有DMA的系统中对数据的传输就显得游刃有余,CPU可以专注于数据处理,数据输入输出这等搬运工干的活就交给DMA来做,DMA和CPU可以共用一片存储区,并且采用乒乓操作进行交互,这样一来,系统性能得到大大提高,CPU的运算能力也可以最大限度的得到发挥。

图2

图3

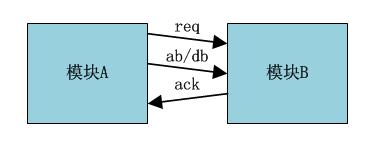

说完CPU系统中的DMA,不得不转移话题来解释下这篇博文的主题“DMA无处不在”。没错,特权同学就是想说FPGA,一个FPGA原型开发系统中“DMA无处不在”。因为一个数据流的处理中,往往是一个流水线式的一刻都不停歇的工作机制。并且任意两个相关模块的通信都有一套握手机制,都有专用的数据地址通道,当然也可以复用,这时候就会涉及到总线仲裁。对于点到点数据传输,特权同学最喜欢的一种简单握手机制如图4所示,模块A要向模块B写入或在读出数据,只要发出req请求,然后送ab/db,直到模块B发出传输完成标志ack信号,那么模块A撤销req完成一次传输。

图4

而对于多点到点的传输,简单的看就如图5所示。需要添加一个仲裁逻辑。

图5

再看整个系统的传输,最简单的顺序流传输就如6所示。

图6

对于稍复杂一些的互联架构的系统,如图7所示。

图7

从上面的几个示意图中不难发现,尤其是图7,系统的利用率很高,可以做到同一时刻整个系统都在运转,并且可以是毫不相关的。这就是FPGA的硬件特性所决定的,软件系统的硬件架构其实就是FPGA设计的精髓,在FPGA系统中的DMA是无处不在的。

/4

/4

用户312110 2011-1-4 10:34

用户574984 2010-8-3 20:01

bitao1983_395643617 2010-7-6 11:06

用户1373959 2010-7-6 02:09