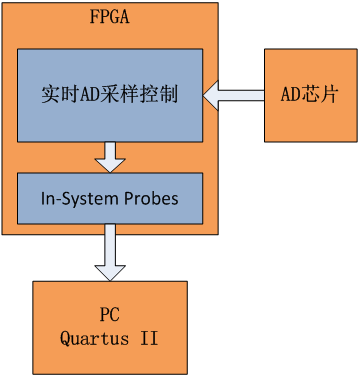

该实例用FPGA的内部逻辑设计一个实时AD采样控制功能,该模块一方面不断的通过SPI接口采集AD芯片TLC549的模拟电压值,另一方面我们例化一个In-System Sources and Probes Editor用于在PC端查看当前采样值。

该实验的硬件平台为特权同学的SF-CY3核心板和SF-BASE板。

SF-CY3 FPGA Cyclone III开发板 套件

http://item.taobao.com/item.htm?spm=686.1000925.1000774.16.mTv0ft&id=22439872377

SF-BASE FPGA套件子板

http://item.taobao.com/item.htm?spm=686.1000925.1000774.6.mTv0ft&id=18922263863

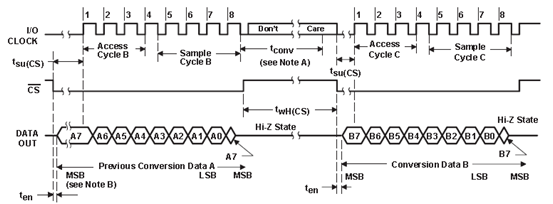

AD芯片TLC549的控制使用了比较简化(单向数据传输)的SPI接口,接口上只需要片选信号adc_cs_n、时钟信号adc_clk和输入数据信号adc_data。控制时序如图所示,只要每次片选有效后产生8个时钟周期依次读取AD采样数据即可。在片选信号拉低后大约1.4us(Tsu)第一个采样数据出现在adc_data上,此时时钟adc_clk上升沿可以采样数据,时钟信号adc_clk的最高频率可以达到1.1MHz。两次数据采样间隔必须大于17us(Twh)。

图7.15 AD芯片控制时序

逻辑实现上,使用了三段式状态机。状态TSUDL和START拉低片选信号并等待第一个转换数据出现在数据信号adc_data上;状态DTRAN进行8个串行输入数据的采样;状态STOP完成一次采样;状态TWHDL延时等待至少17us,保证两次数据采样有足够的时间间隔。

因为In-System Sources and Probes Editor是Quartus II中的一个IP核,所以我们需要先对其进行设置添加,然后例化到我们的代码中。

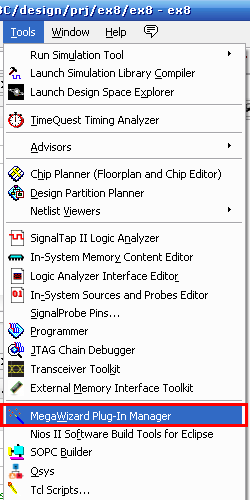

点击菜单栏ToolsàMegaWizard Plug-In Manager。

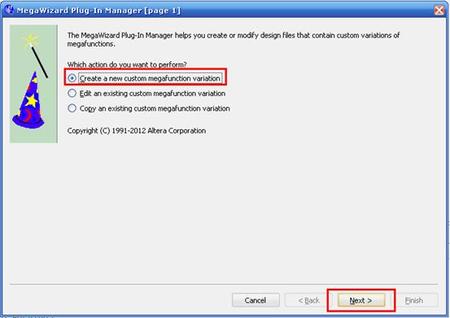

选择Create a new custom megafunction variation。

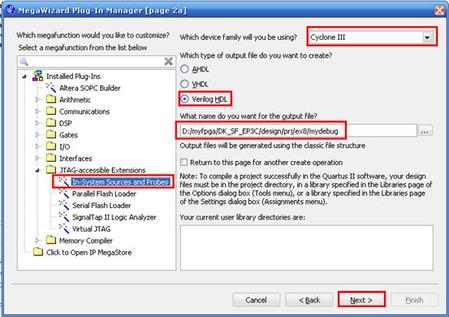

在MegaWizard Plug-In Manager中,做如图所示的设置,注意在What name do you want for the output file中,需要输入一个该代码的文件名,如这里在工程目录ex8后面命名mydebug。最后点击Next进入下一步。

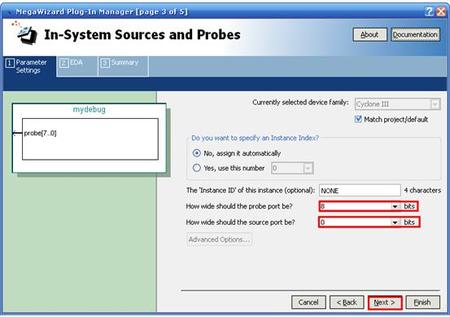

如图所示,我们需要在In-System Sources and Probes Editor配置页面中,设置probe port为8bits,source port为0bits。Probe的功能是读出(对于工程设计为输出)我们的FPGA设计中的某些寄存器,而source则是写数据(对于工程设计为输入)到FPGA设计中。本实例是要实时监控查看输出的AD采样值,所以选择probe。完成设置选择Next。

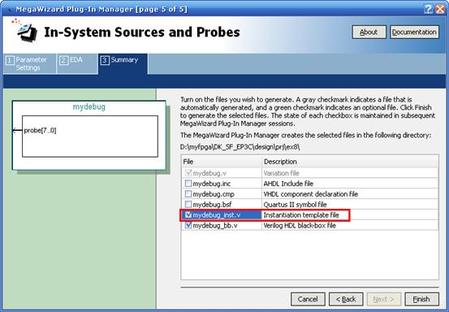

第二步EDA不需要做设置,我们来到Summary配置页面,注意要勾选mydebug_inst.v文件,这个文件里面有In-System Sources and Probes Editor的例化模板。完成这些设置后,点击Finish完成所有配置。

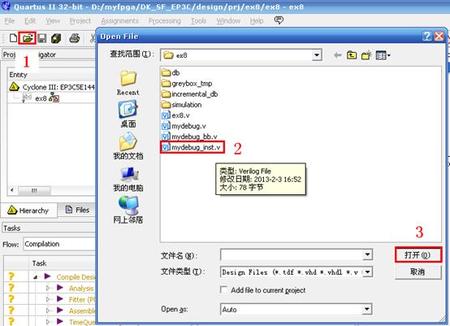

回到Quartus II界面,我们点击Open File快捷按钮,找到工程目录ex8下的mydebug_inst.v文件,打开它。

我们可以看到如下的代码,可以将它复制到工程源码中,对括号内的信号做相应的映射更改。

mydebug mydebug_inst (

.probe ( probe_sig ),

.source ( source_sig )

);

/5

/5

用户1759356 2014-5-17 11:55

用户204178 2013-5-15 23:55

用户377235 2013-4-23 22:31