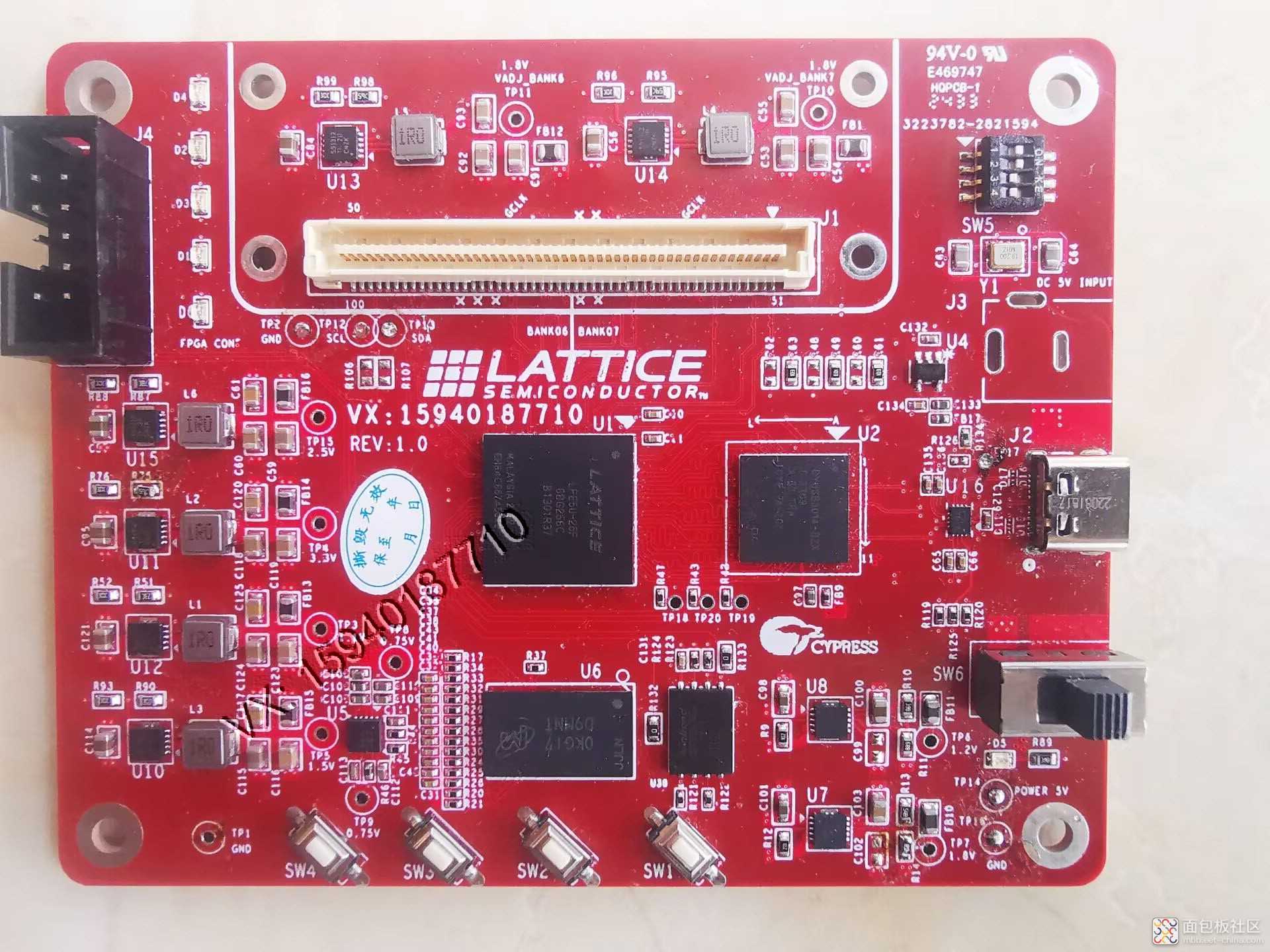

一、基于SPARTAN6的USB3摄像头开发板已经完成有几年了,为适合最近的项目需求,又重新设计了一款基于ARTIX7的USB3电路板。总体设计目标基本一致,都是想胜任通用USB3的数据采集及工业相机的开发,所以电路板的硬件结构都一样,都是基于FPGA+DDR3+USB3的结构。FPGA选择的是484引脚的XC7A35TFGG484的,DDR3选择的是MT41J128M16,用来做图像数据的帧缓存,USB3芯片还是常用的CYUSB3014。电路板总体结构如下: 二、电路板上的主要部分简单介绍如下: 1、FPGA主芯片,A7的XC7A35TFGG484的,用做主控芯片; 2、USB3.0芯片,型号是CYUSB4014BZXI,USB3数据传输的; 3、DDR3芯片,型号是MT41J128M16,用做图像数据帧缓存的; 4、外部连接器,可以将摄像头子板的,如IMX178的,IMX287的,IM273的子板。引脚是100PIN的,分别连接到了FPGA的两个独立的BANK上,分别是BANK34和BANK35上。 5、USB3连接器,TYPE-B接口,比较结实的这种连接器。后面的USB4开发板会全部转向TYPE-C接口; 6、电源芯片两个,LDO类型的,提供给USB3芯片3.3V和1.2V,独立供电; 7、FPGA的电源芯片,三个电压为别是内核的1.0V,DDR3的1.5V和独立的3.3V; 8、FPGA的GTX电源芯片三个,分别是1.0V、1.2V和1.8V; 9、BANK35的单独供电芯片,默认是1.8V,用户可以自己更改这个电压; 10、BANK34的单独供电芯片,默认是1.8V,用户可以自己更改这个电压; 11、调试用的4个LED指示灯,还有一个FPGA配置好的指示灯; 12、调试用的4个按键; 13、USB3用的启动方式拔码开关,可以设置成从USB3启动还是从SPI FLASH芯片启动。8脚SOP芯片是SPI FLASH芯片; 14、外部供电及电源开关。电路板一般从USB3电缆取电就行; 15、FGPA的JTAG下载接口; 16、DDR3的端接电压芯片; 三、以下是电路板连接摄像头子板的示意图 上图摄像头是用的IMX273或者是IMX287,当然也可以接之前的IMX178。这些摄像头都是Sub-LVDS接口的,开发板也可以MIPI接口的摄像头,后面再作介绍。 四、电路板硬件准备好了,后面会重点说明一下IMX273摄像头的开发。类似的方案已经用在了多个项目上了,下面简单介绍几种应用。一是应用于口腔扫描仪,二是标准的工业相机。后面会有专门的帖子说明这方面的应用。 五、除了前面介绍的ARTIX7硬件电路板,适合项目应用的还有K7的以及ECP5的工业相机开发板。后面还会推出国产易灵斯FPGA的USB3.2开发板。 这是一个基于K7的FPGA+DDR3+USB3的通用开发板,硬件结构基本上和前面的电路板是一致的。 这是一个基于LATTICE的FPGA的开发板,具体系列是ECP5的,设计这款开发板主要目的是为了开发工业相机。ECP5的FPGA可以支持多种摄像头的接口,包括LVDS、Susb-Lvds、SLVS和MIPI的,当然也能用做SLVS-EC的接口。关于SLVS-EC接口,后面会抽时间开发一下。 良子USB,20250405 专注USB3.0、FPGA、PCIE、定制UVC摄像头 VX:15940187710

标签: usb3

标签: usb3