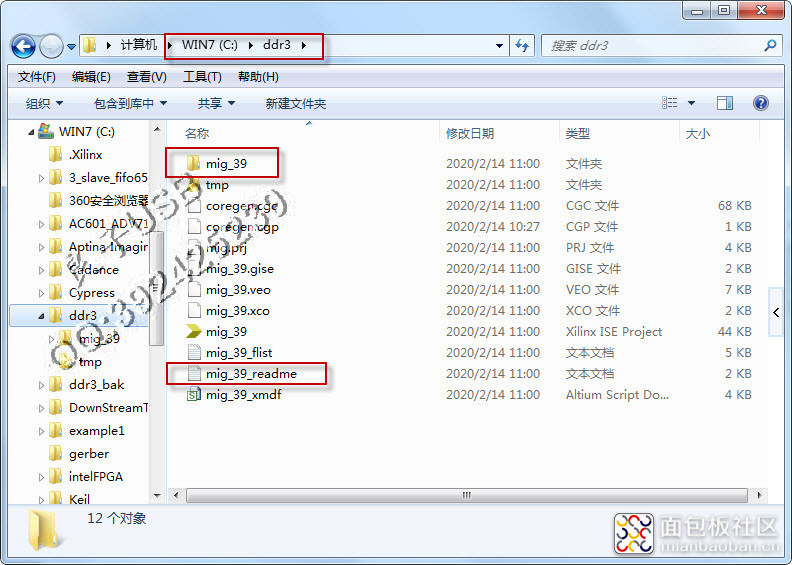

一、前面通过MIG生成了DDR3的IP核,同时生成了一个用于测试的工程test 。只不过这个test工程比较晦涩,并不是所见即所得,还得经过一些隐秘的步骤,才能呈现出来。前面生成IP核后,在ddr3文件夹内生成了1个mig_39目录,以及一些文件,如下图:其中有个mig_30_readme文本文件,需要看一下。

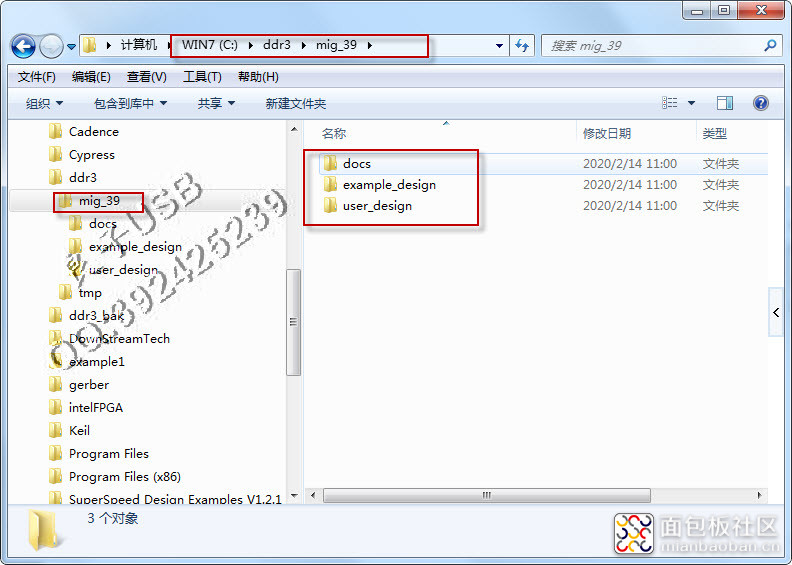

二、打开目录mig_39,里面含有3个目录,如下:

1、docs目录,里面含有两个DDR3开发的文档UG416和UG388。这两个文档需要仔细看,所有SPARTAN6与DDR3相关的内容都在这两个文档里。需要至少看十篇。

2、example_design目录,MIG提供的测试例程test,或者叫traffic generator。这里主要就是实际测试这个test工程。

3、user_design,这个目录是用户需要集成到自己的项目中的。

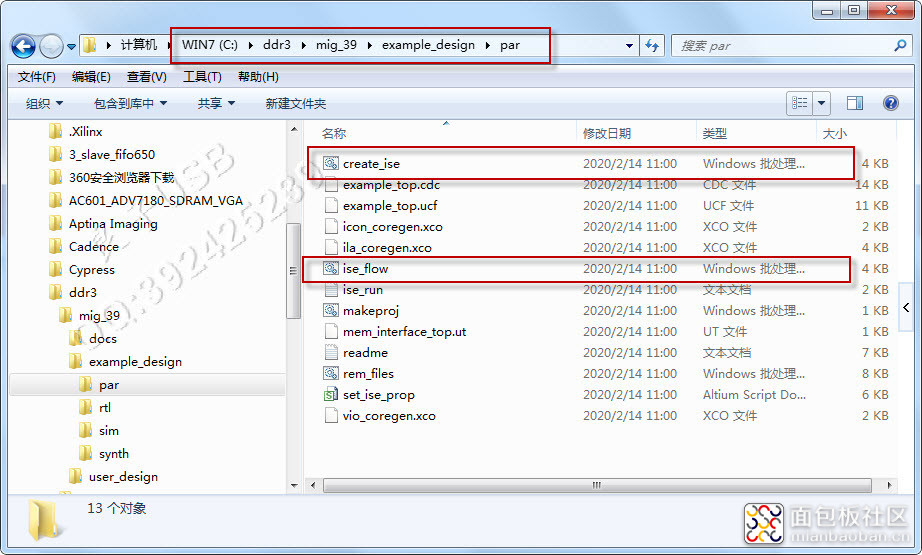

三、开始创建test工程。打开如下的目录,里面根本没有test工程的影子。先找到两个批处理文件,如下 ,直接双击不行,需要在命令行下进行,

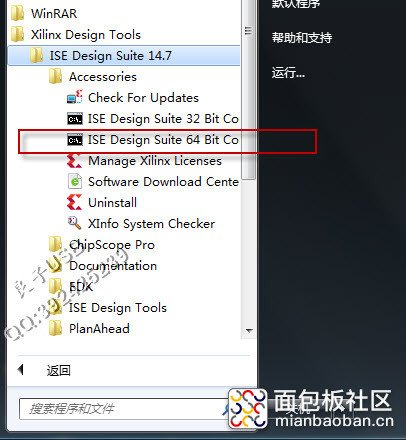

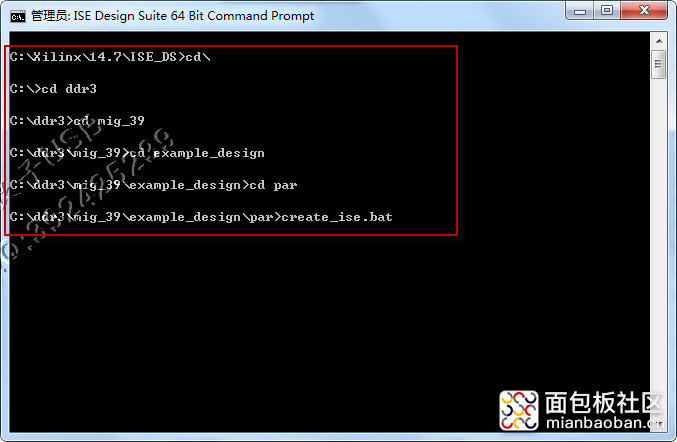

四、打开ISE14.7自带的64位命令行程序,如下:

五、输入如下DOS指令,定位在前面的目录C:\ddr3\mig_39\example_design\par下,再运行create_ise.bat文件,

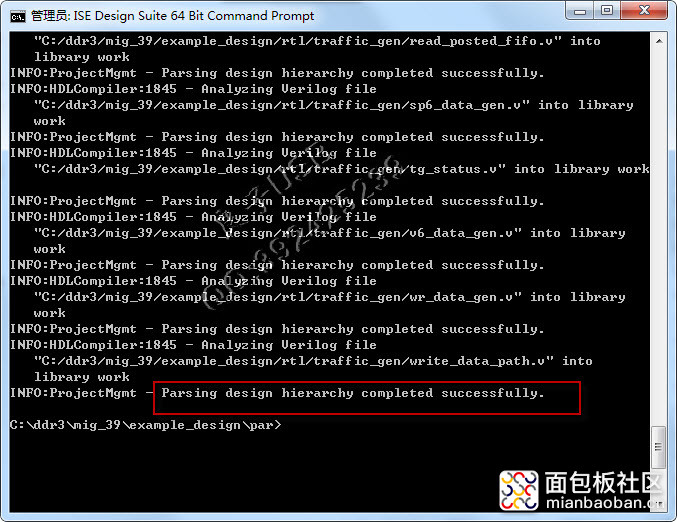

六、经过一段时间,test工程成功建立。如下,

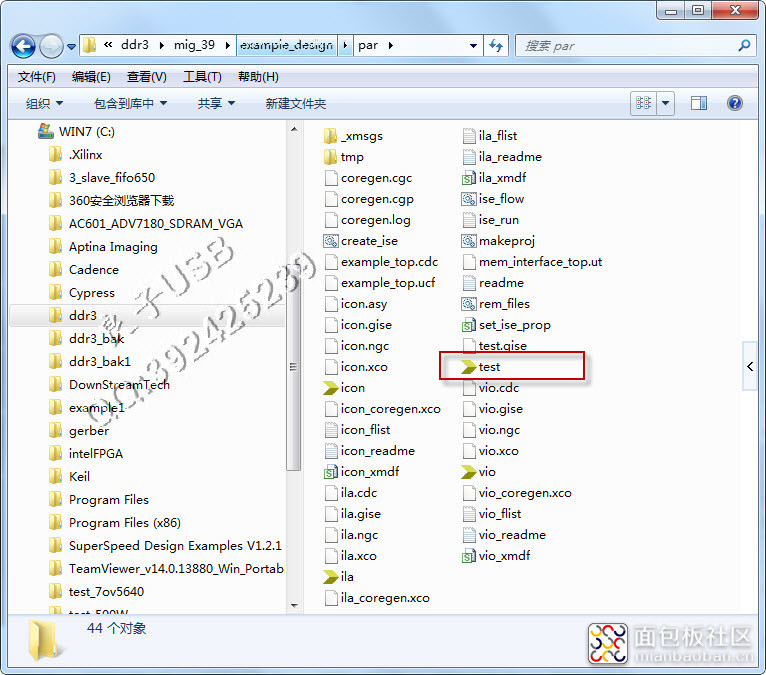

七、回头再看C:\ddr3\mig_39\example_design\par目录,test工程已经出现了,如下 :

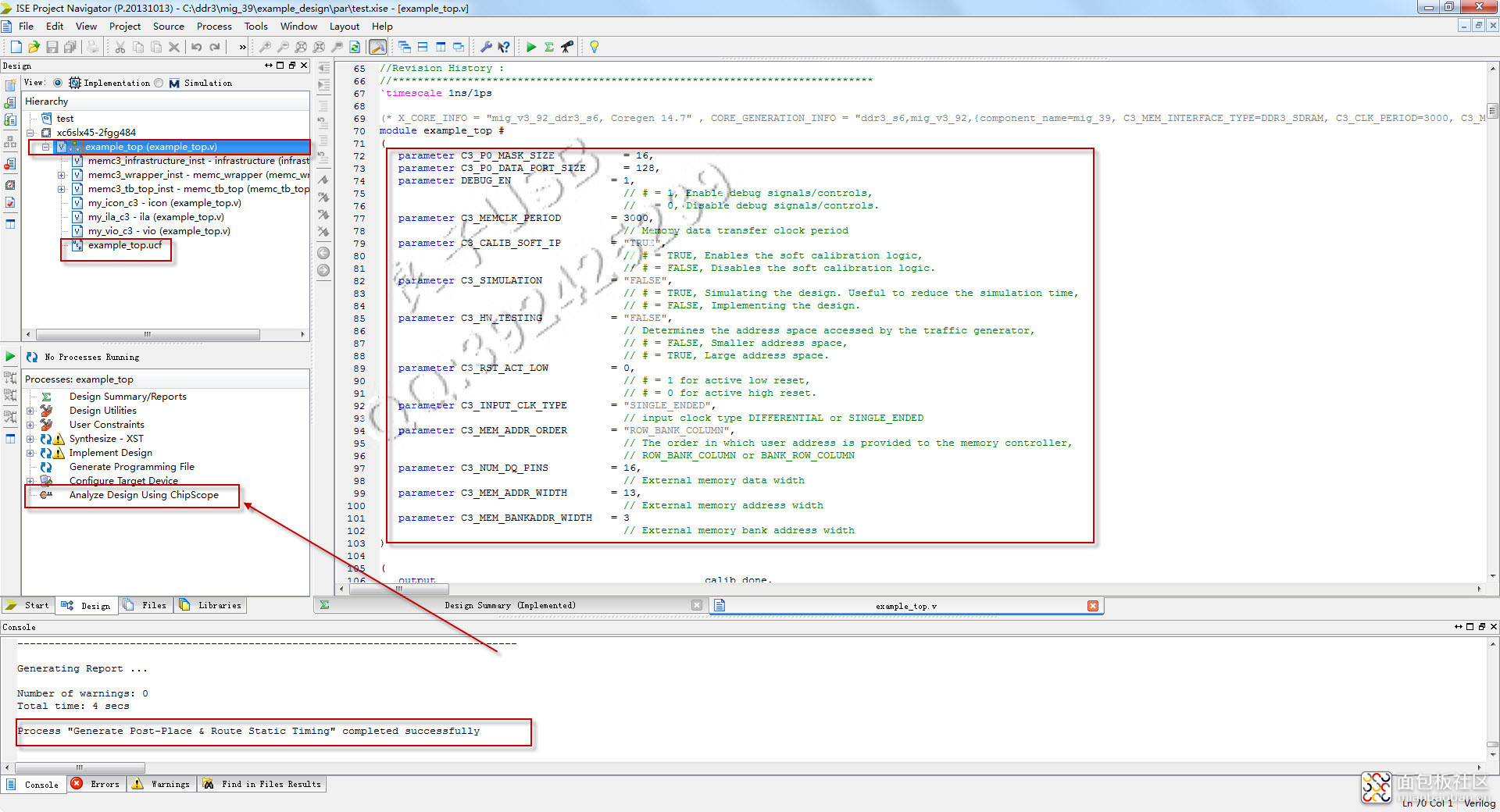

八、直接双击打开这个test工程,如下:

如上的test工程可以正常编绎成功。

1、上图中左侧的文件管理窗口,已经包含了.ucf约束文件,待会会进一步修改这个文件,以便和我的硬件开发板对应;

2、接下来会用CHIPSCOPE软件与实际电路板连接,观测实际的波形;

九、打开.ucf约束文件,修改了LED引脚以及时钟相关部分,再重新编绎工程,成功后连接电路板。

(具体修改部分见下一篇文章。)

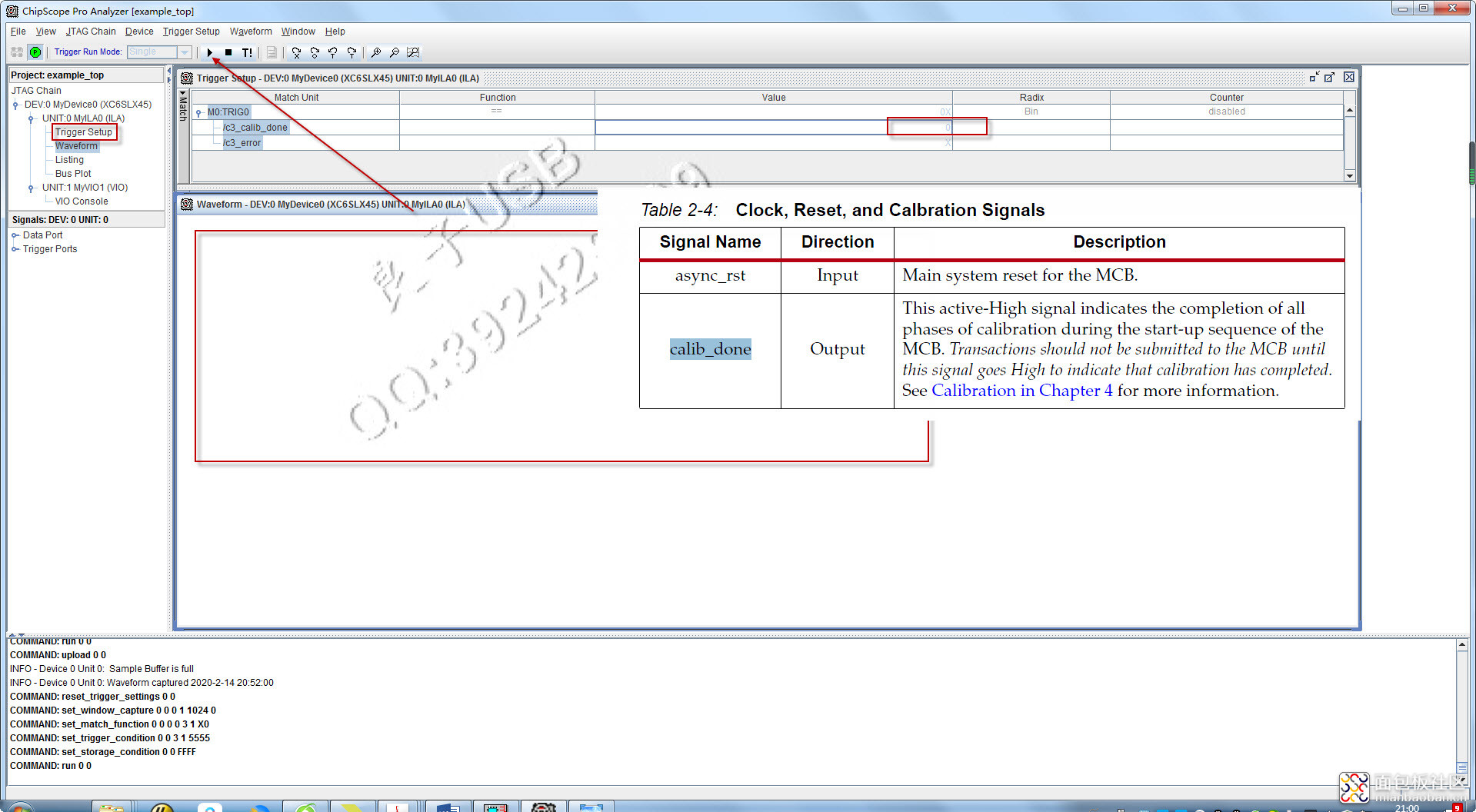

十、连接成功后,直接点Trigger运行,成功如下:

十一、这里重点关注DDR3初始化是否成功的信号c3_calib_done。DDR3初始化成功,c3_calib_done信号为高;DDR3初始化失败,c3_calib_done信号为低。打开Trigger setup窗口,设置c3_calib_done为0,看初始化是否失败?程序运行后,没有触发到任何波形,说明DDR3初始化成功。

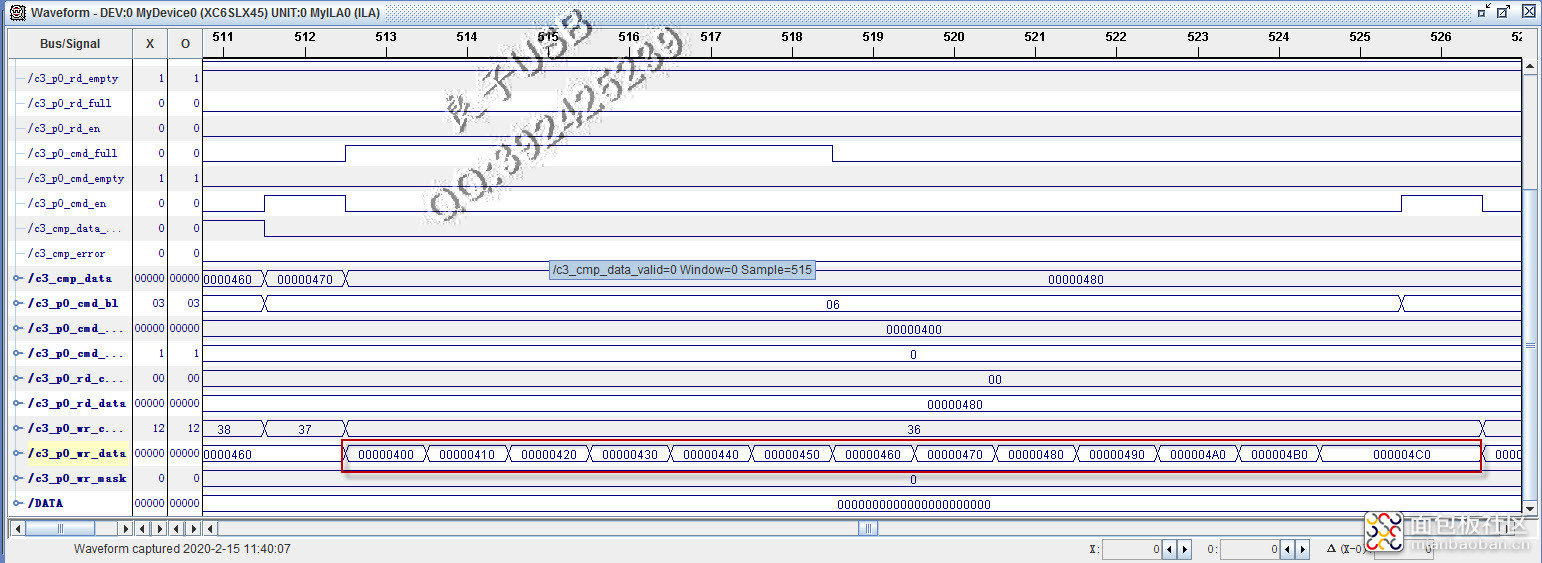

十二、进一步放大c3_p0_wr_data信号,如下,可以看到数据非常有规律,说明成功。

至此,DDR3已经正常运行了。后面,会对这个test工程详细分析。

良子USB,20200215

专注USB3.0、FPGA、PCIE、定制UVC摄像头

QQ:392425239

/5

/5

文章评论(0条评论)

登录后参与讨论