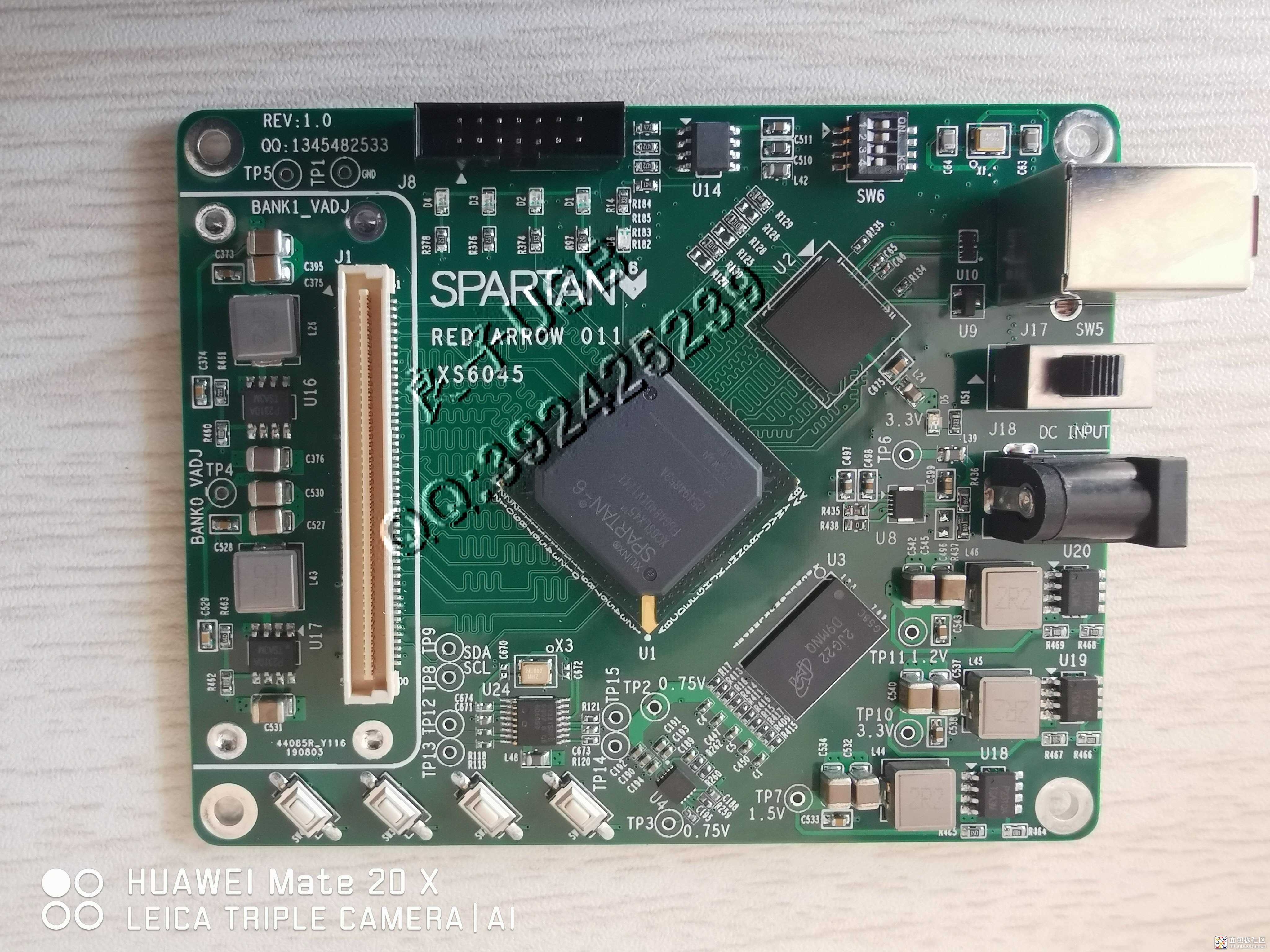

一、前面介绍了含有DDR3的硬件开发板,以下内容都是基于这块FGA 开发板所进行的,生成的DDR3控制器直接可以下载到硬件电路板中实际验证,观察结果,加深理解学习。SPARTAN6芯片内部含有控制DDR3的硬核MCB,这个硬核还需要从软件上进行管理,这个软件即是MIG,以下是通过MIG生成DDR3的IP核的过程。生成过程主要是通过帖图体现的,为了创建一个可以参考的实例,帖图会比较详细,适合刚入门的使用,高手可以忽略。

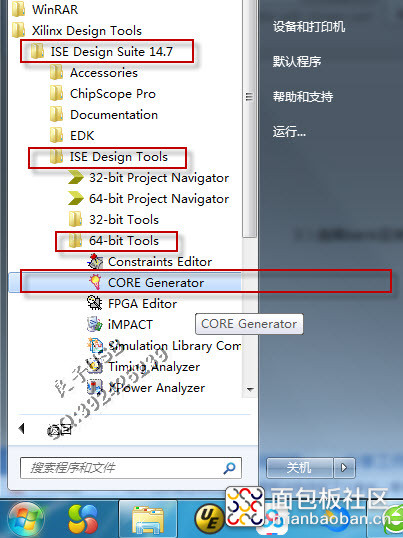

二、如下图:先启动ISE14.7的IP核生成器CORE Generator,

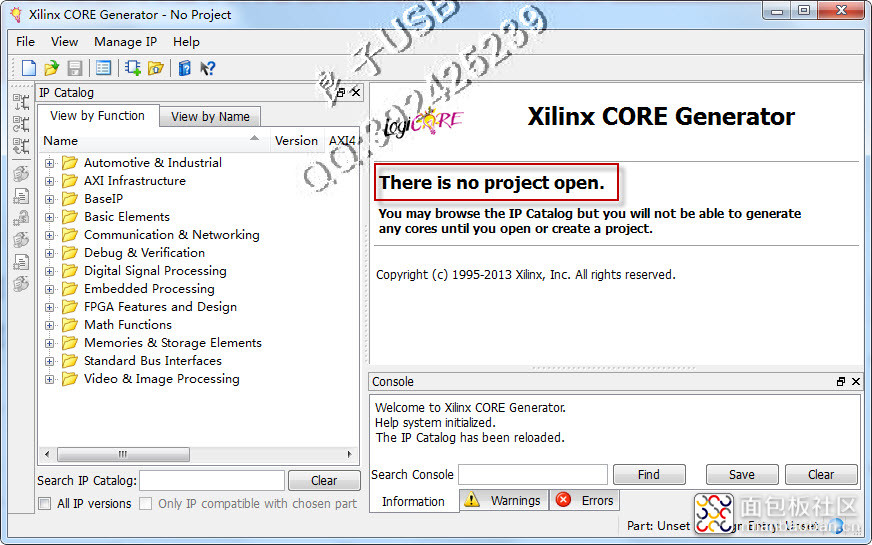

二、IP核生成器CORE Generator启动后如下:

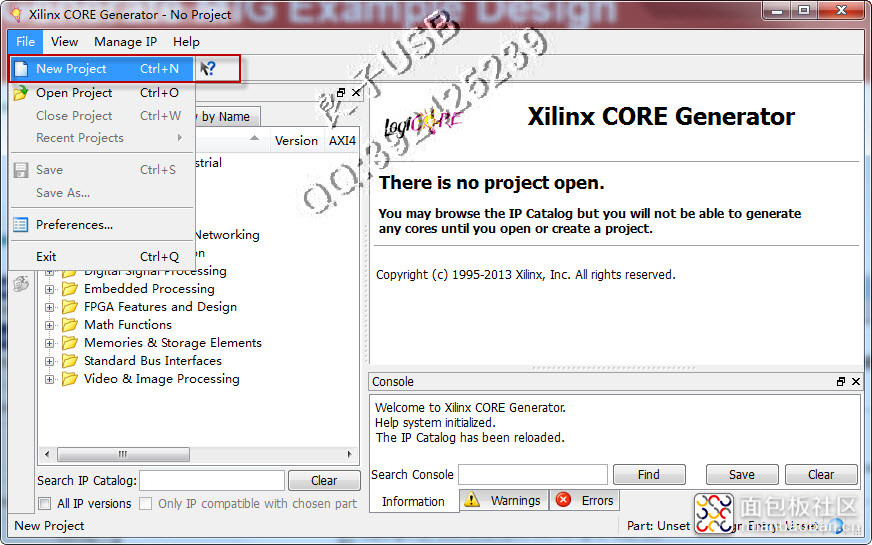

三、在IP核生成器CORE Generator里先创建一工程,如下:

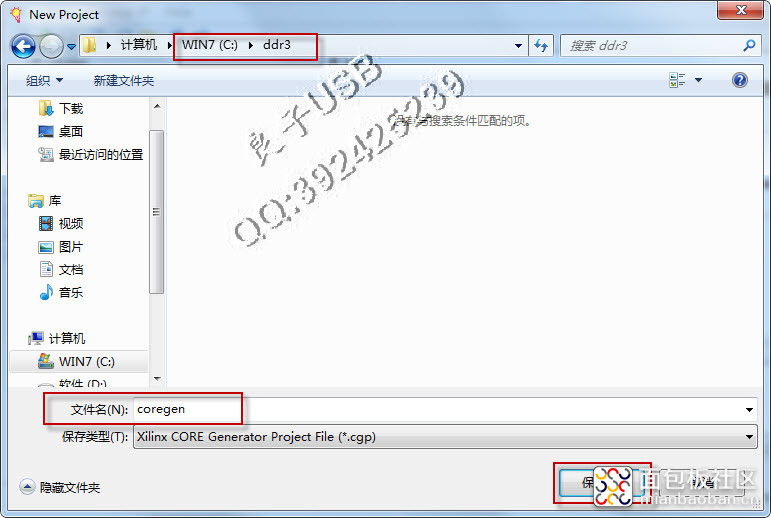

四、在C盘里创建一文件夹ddr3,文件名为corgen,如下,

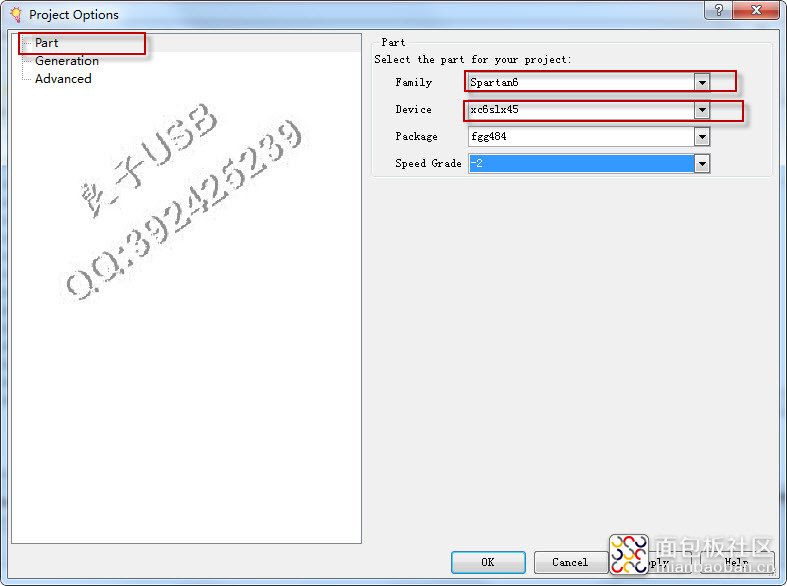

五、选择硬件电路板对应的FPGA型号,在Part选项中,选择SPARTAN6,XC6SLX45,封装为484引脚的,速度等级为-2的,如下:

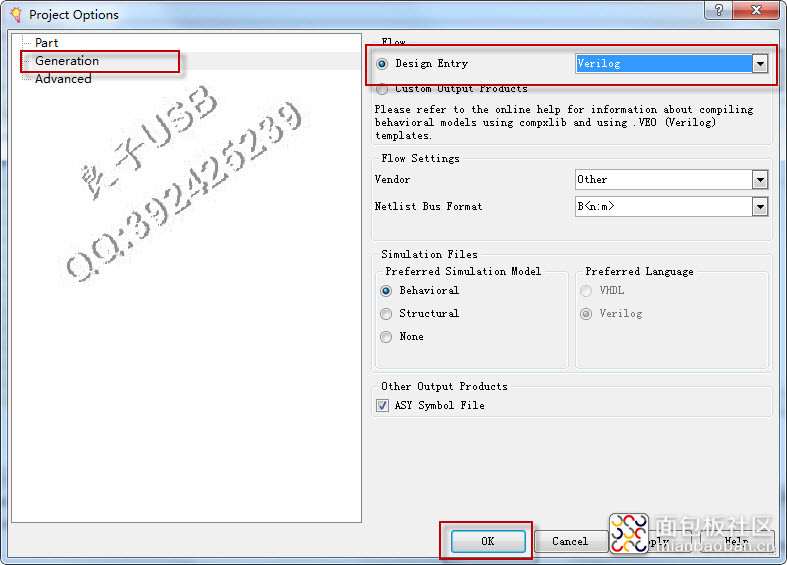

六、切换Generation选项中,Verilog开发语言,如下:

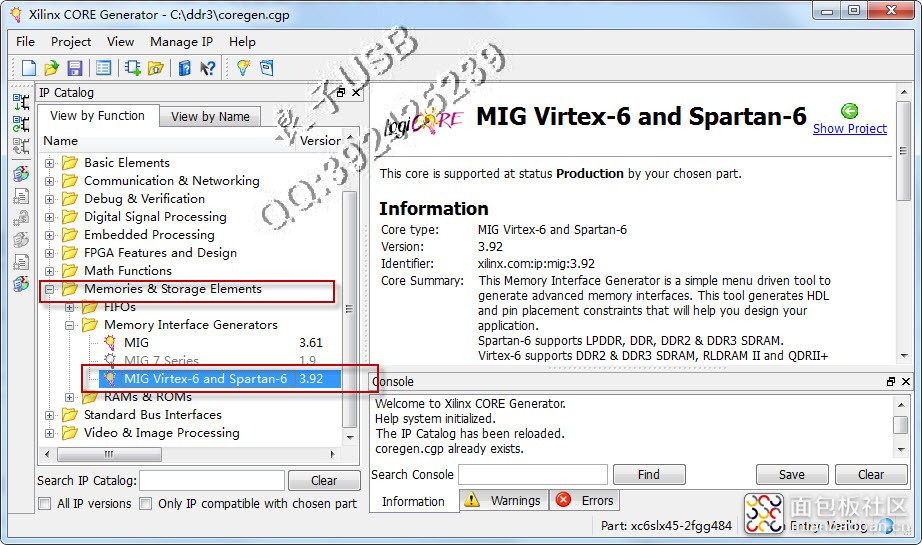

七、按下图找到MIG的IP核,双击打开,

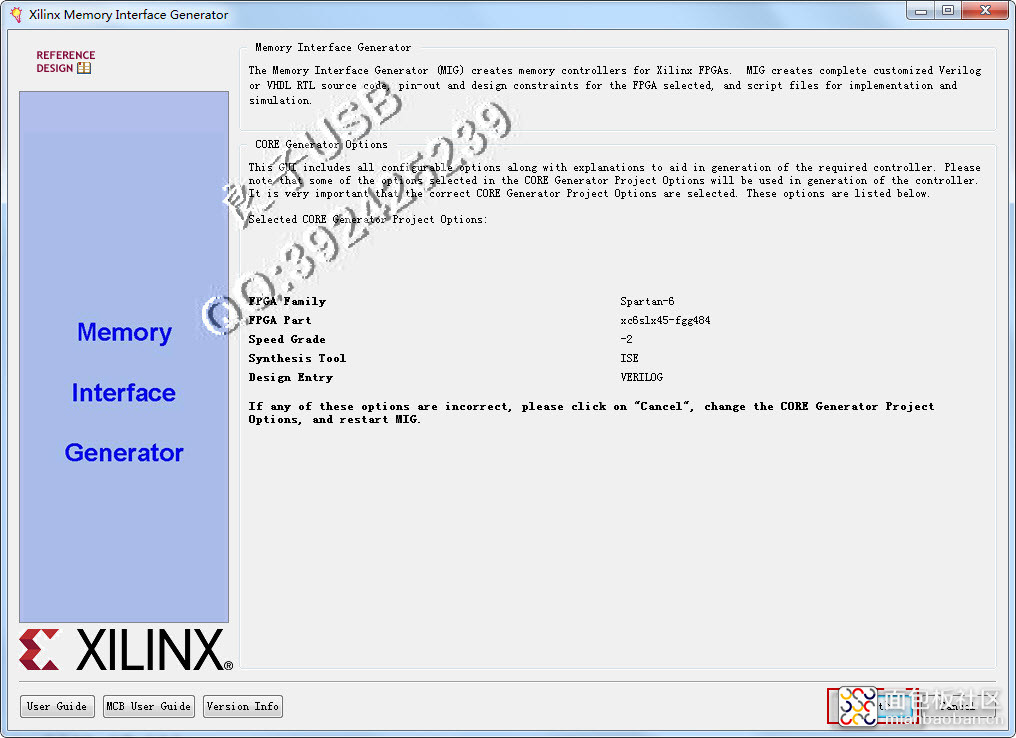

八、启动MIG画面如下,点下一步,

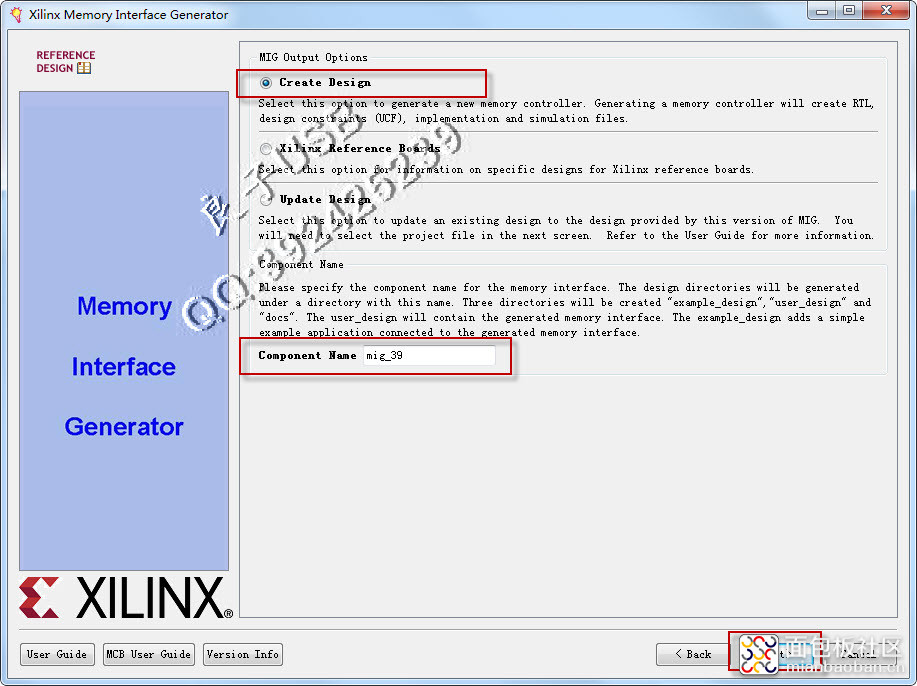

九、创建一个新的IP核 ,名字为mig_39,如下:

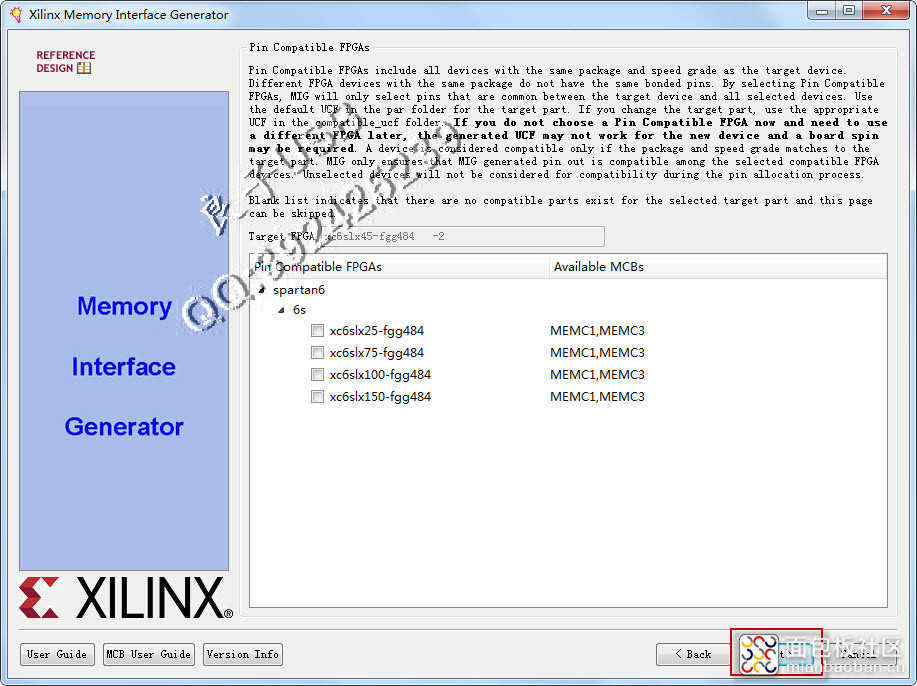

十、这一步选择兼容的FPGA型号,这里不作任何选择,直接下一步,

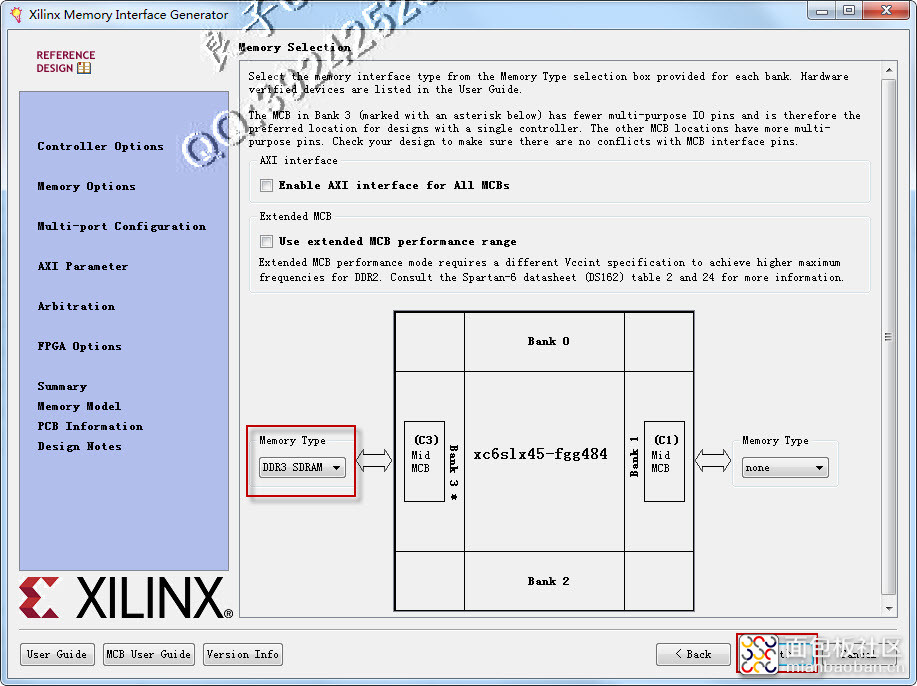

十一、这里选择BANK3上的MCB控制器,

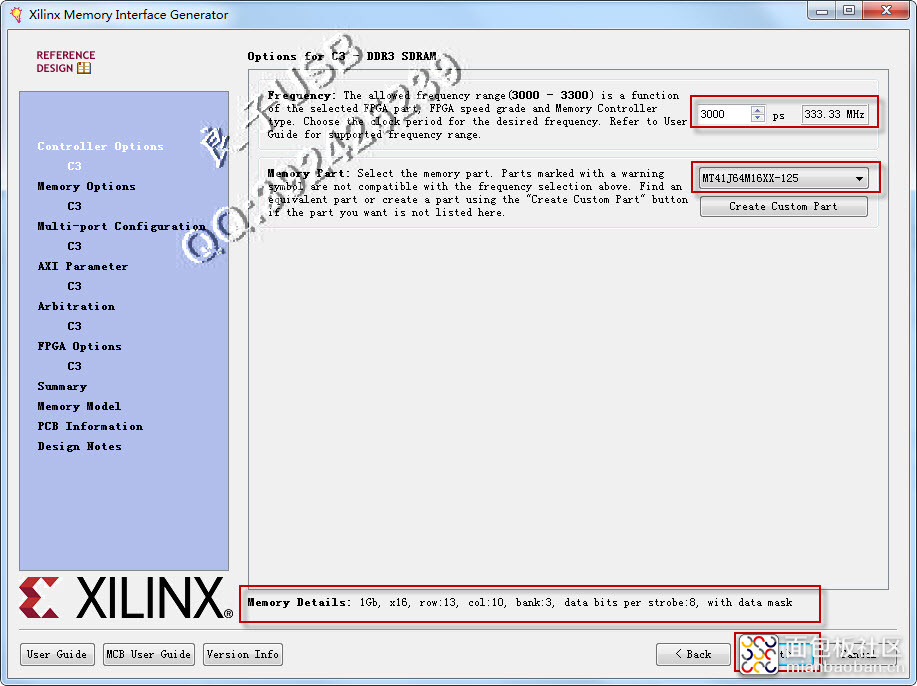

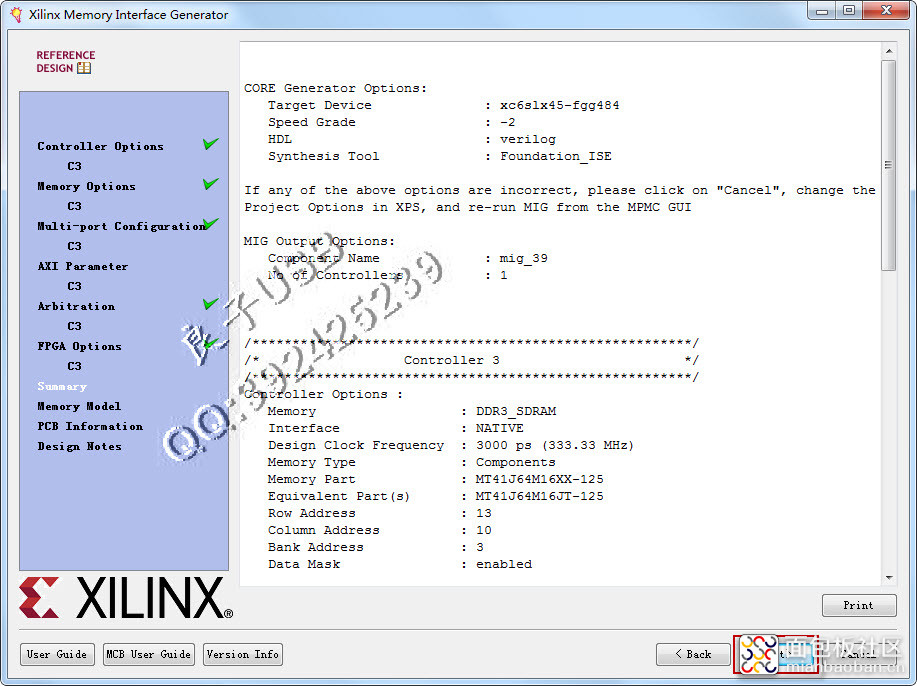

十二、这里设置DDR3的时钟频率,工作在667M,一半就是333.3M;DDR3的实际型号为MT41J64M16JT-125,64M*16的,

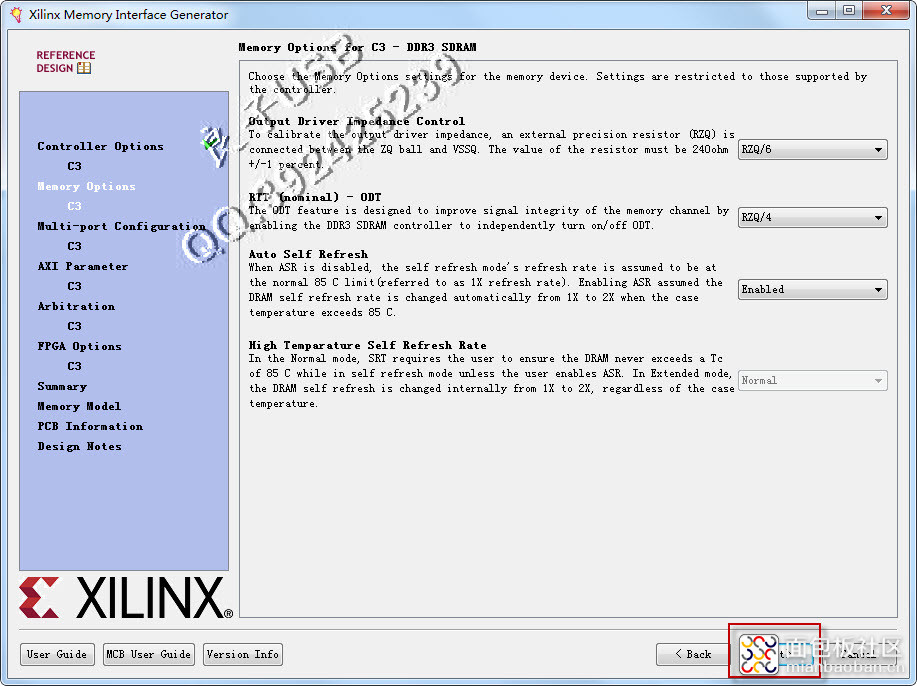

十三、这里默认的就可以,直接下一步,

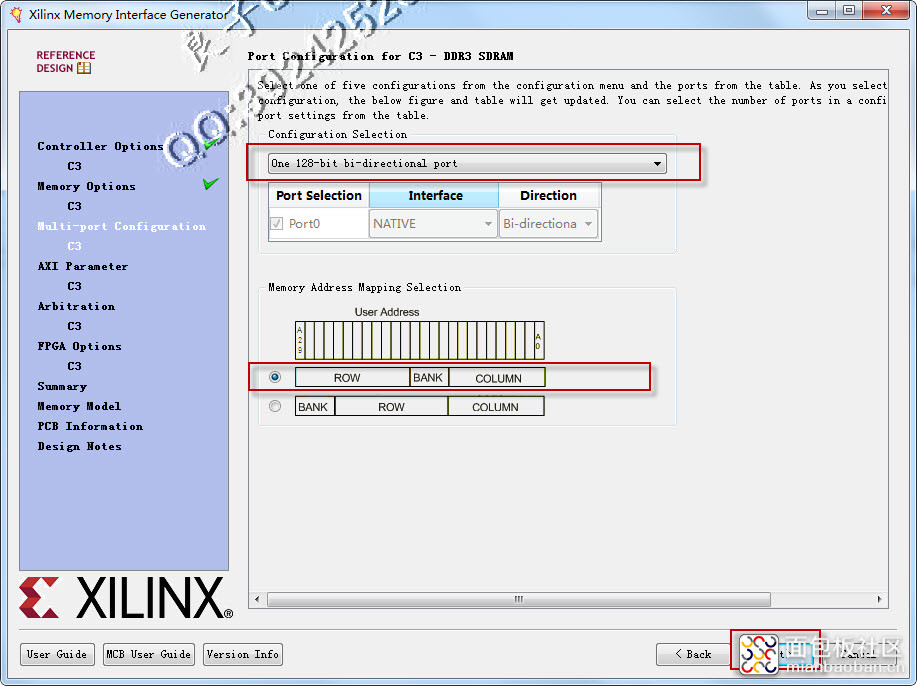

十四、选择一个128位宽的双向接口,寻址方式为ROW_BANK_COLUMN方式,

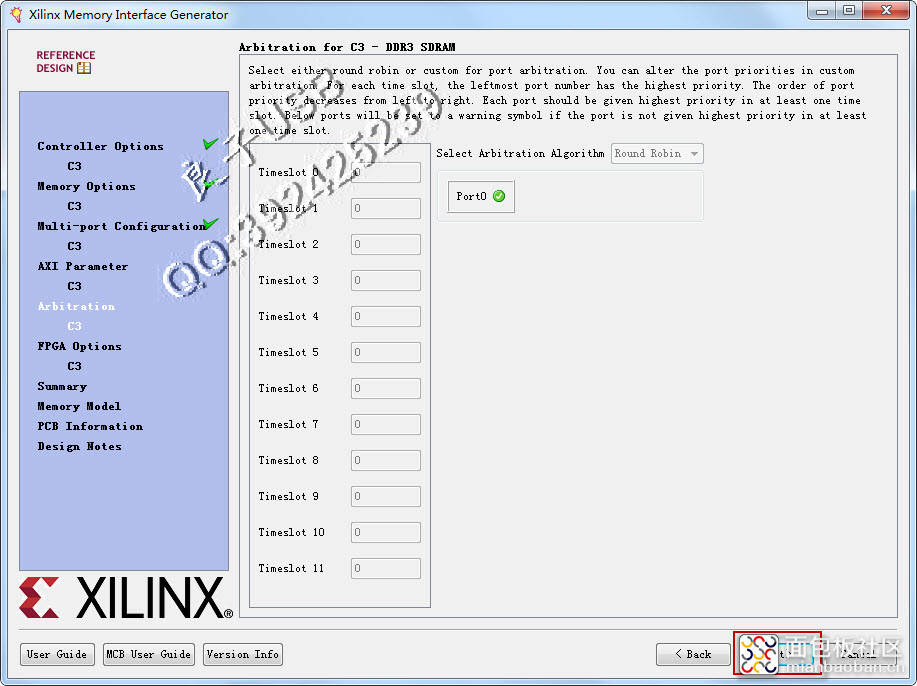

十五、默认、下一步,

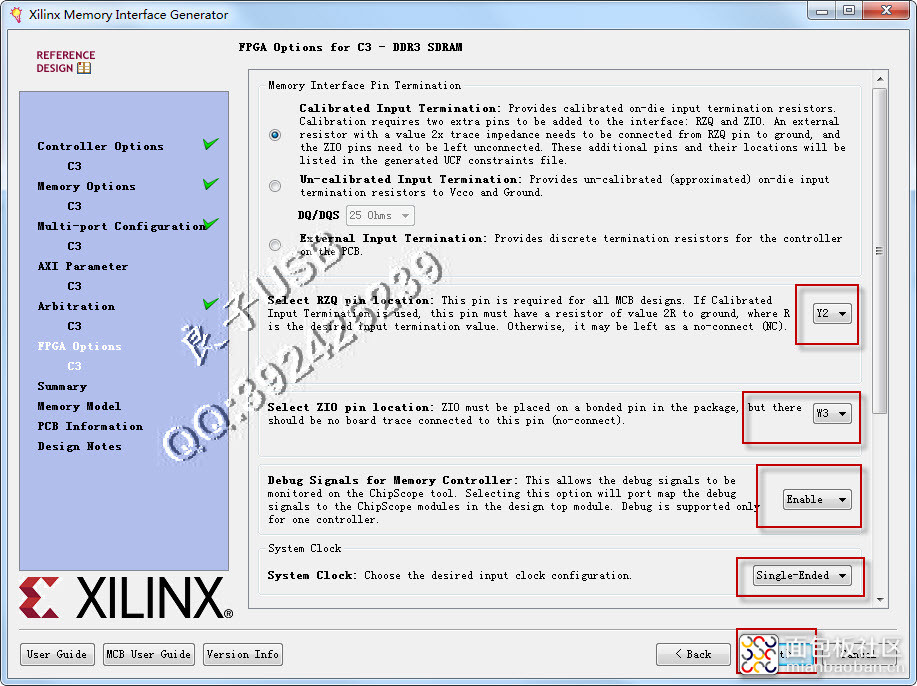

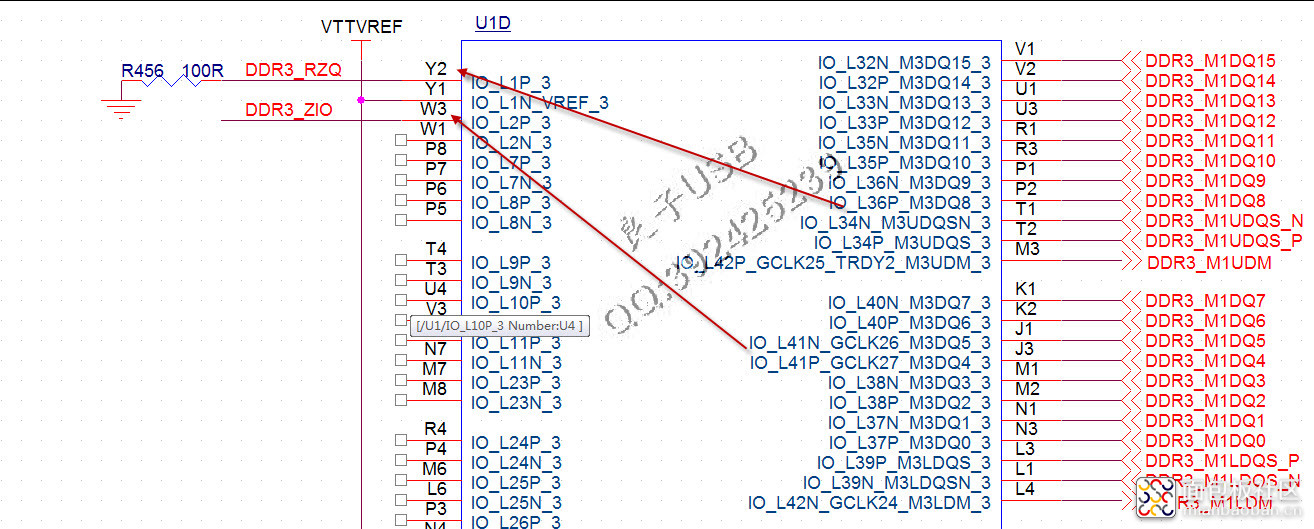

十六、这里选择DDR3上电后校准的几个引脚,要对照实际的硬件原理图设置,RZQ电阻选Y2,ZIO引脚选W3,使能DEBUG调试,后面就用CHIPSCOPE调试,选择单端时钟,直接点一下步,

十七、上面的硬件设置,是和我的硬件电路板对应的,如下:

十八、MIG设置总体完成了,这一步是汇总相关的信息,直接下一步,

十九、点同意,点下一步,

二十、点下一步,

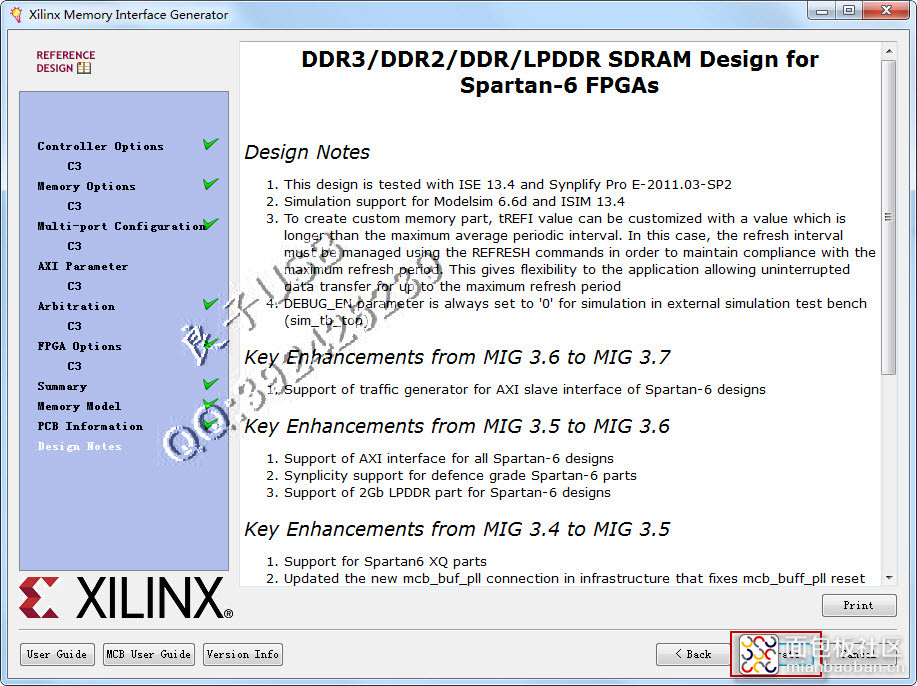

二十一、点Generate生成IP核,

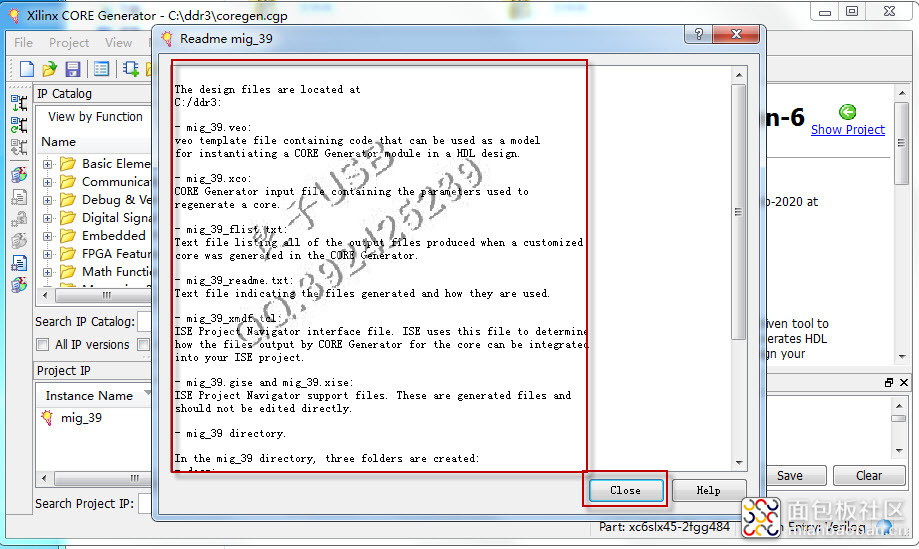

二十二、IP核成功生成,点Close,结束。

至此,DDR3的IP核生成完毕。

下一篇将生成的TEST工程下载到实际硬件电路板中运行一下。硬件电路板如下:

良子USB,20200214

专注USB3.0、FPGA、PCIE、定制UVC摄像头

QQ:392425239

/4

/4

文章评论(0条评论)

登录后参与讨论