前面生成了test工程,用于测试DDR3。在实际下载测试前,还需要修改一下exapmle_top.ucf约束文件。以下记录了修改的要点:

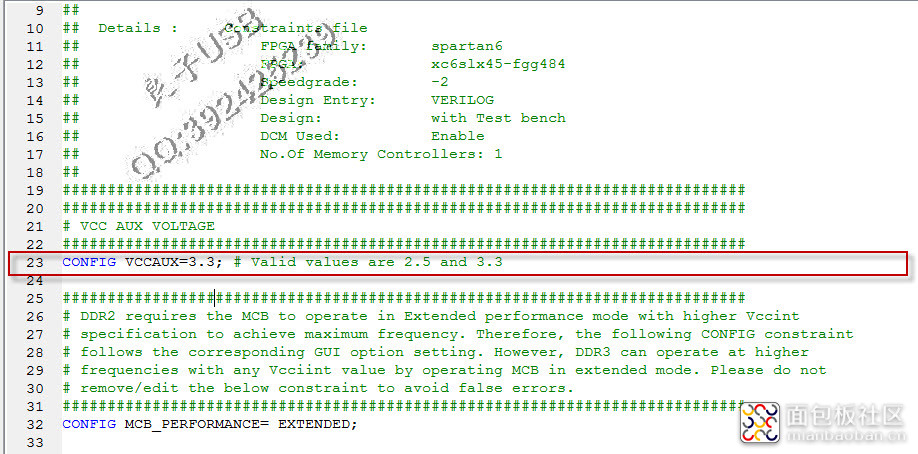

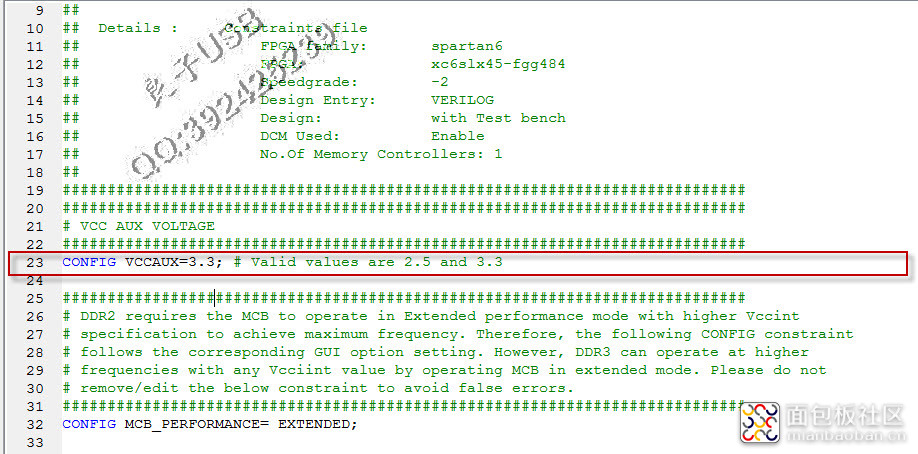

一、修改文件exapmle_top.ucf的第23行,修改VCCAUX的供电电压,从2.5V修改为3.3V,如下:

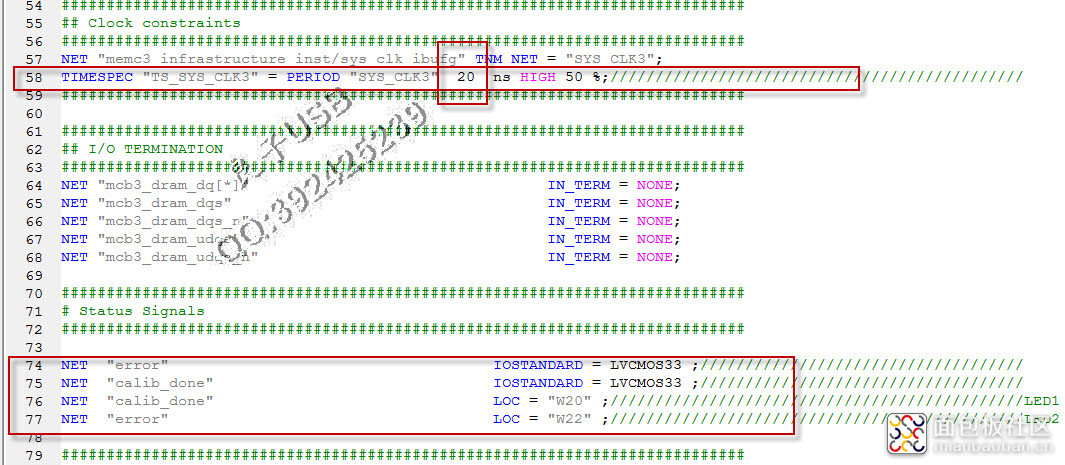

二、修改文件exapmle_top.ucf的第58行,输入晶振的周期修改为20nS。电路板上设计为单端晶振,3.3V供电,频率为50M。

三、修改文件exapmle_top.ucf的第74、75行,处理两个关键信号error和calib_done所在BANK的供电电压,修改为3.3V。另外,这两个信号实际连接到了W20和W22引脚上,也需要根据硬件电路板对应修改一下,如上面76、77行。

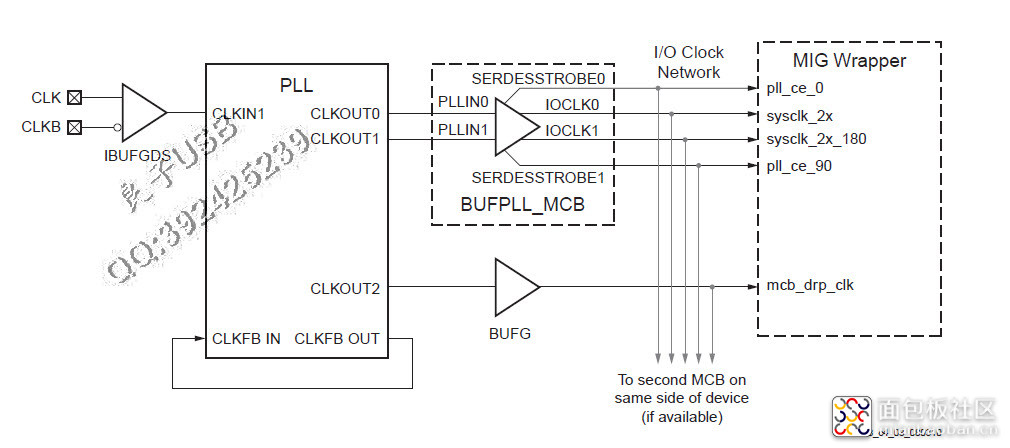

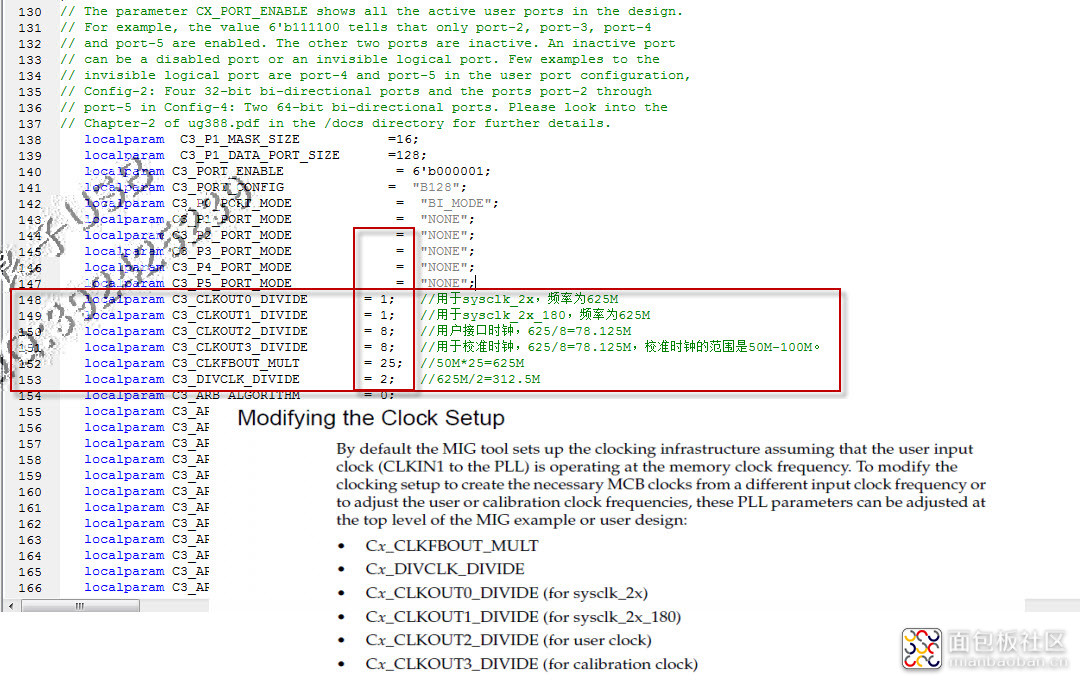

四、修改主文件exapmle_top.v的148行时钟相关部分。这部分内容比较复杂,需要熟悉ug388的时钟及PLL部分,帖图如下 :

上图中左侧是差分时钟输入的,先经过一个IBUFGDS原语缓冲,再接到PLL输入端。实际硬件电路板为单端时钟,不是差分时钟,这部分可以省略。PLL输出有三路,分别为CLKOUT0、CLKOUT1和CLKOUT2,前两个时钟经过BUFPLL_MCB后,生成2倍速的sysclk_2x和sysclk_2x_180,这是MCB工作的两个主要时钟。假定DDR3时钟频率为312.5M,2倍速为312.5M*2=625M。

具体修改如下 :

上图中的汉字注释部分,对于MCB用到的几个时钟已经说明的很清楚了,右下部分是出自于ug388中的第39面。

经过以上修改, 工程test已经和实际硬件电路板对应起来了,程序可以实际下载到电路板上运行了。

test工程的具体代码分析,见后面的文章。

良子USB,20200215

专注USB3.0、FPGA、PCIE、定制UVC摄像头

QQ:392425239

/4

/4

文章评论(0条评论)

登录后参与讨论