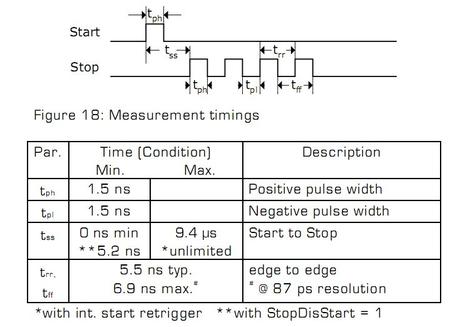

ACAM的TDC-GPX是基于时间戳的TDC,也就是说其根本原理还是基于延时线即delay-line。其手册里没有详细介绍其原理(这是人家的机密),只是简单简单其测量精度来源于内部传输延时(internal propagation delay)。下图是TDC-GPX在I模式下的技术指标:

这个表提示我们,如果我们要设计基于FPGA的TDC,你将要提供的指标参数要与上述指标看齐,至少需要提供上述指标的测试报告吧(Test Report)。

这个图还有一个最最重要的参数没有给出,就是时间测量精度。其实这个测量精度就是取决于延时线每个延时单元的延时,如果是进行基于FPGA的TDC设计,我们首先映入脑海的就是逻辑延时或者门延时。在前面介绍TDC的时候有关于延时线的种类中有介绍门延时。在FPGA范畴里也有一个门延时的概念,在当年的FPGA里给客户看到最新单元是LE(logic element),ALTERA有个LCELL的东东,人们最先想到的是用它来作为延时线的基本延时单元。但是我们知道LCELL这个东东除了前面提到的门电路延时线里的缺点以外,还有两个重要的缺点就是基本延时时间太大,所以就是设计出来TDC的精度也不高,另一个缺点就是基于LCELL的延时线每次编译的结果会不一样,因为软件会随机的分配每一个LCELL的位置,当然设计者也可以通过添加位置约束来控制LCELL的位置,但是这将是一项繁琐的工作,后面我们介绍为何这是项繁琐的工作。

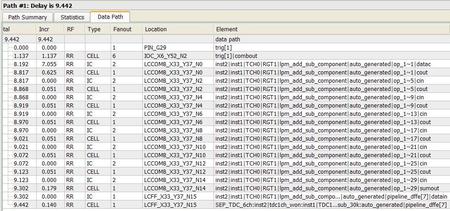

既然LCELL不是最佳的延时单元,那么FPGA内还有什么可以作为最佳的延时单元呢?答案是进位链(carry-chain)。为什么carry-chain可以呢?这里卖个关子,这里先给出carry-in到carry-out的延时时间,下图是在ArriaGX上得到的此时间:

看出端倪了吧,哈哈,清一色的51ps呐。51ps延时时间,意味着51ps的时间测量精度,想想大部分需要TDC的应用都应该能满足了吧!!!

/5

/5

文章评论(0条评论)

登录后参与讨论