TDC即Time to Digital Convertor,用来完成时间间隔测量,这里整理了前人的论述。

1. TDC的基本分类

图1

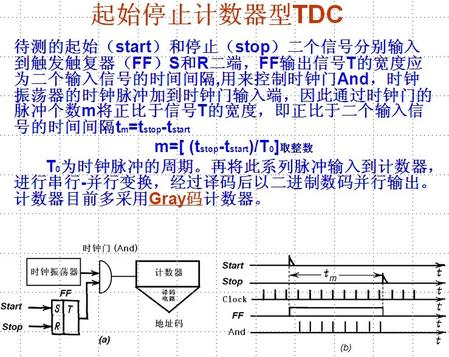

2. 什么是起始停止计数器型TDC

图2

•直接计数器型TDC的优点是电路简单,大尺度时间测量范围,且全数字化,易于集成。

•时间精度(一个LSB代表的时间间隔量)受到时钟频率以及它的稳定性限制,因为高时钟频率(1GHz以上)在工艺和电路结构上要付出很高代价。这种TDC的时间精度在ns量级。

•采用自激时钟振荡器会造成2 T0的误差,采用它激时钟振荡器误差可以减小到1 T0,但是在一般情况下,振荡器起振阶段,频率和幅度不稳定,也会带来误差。

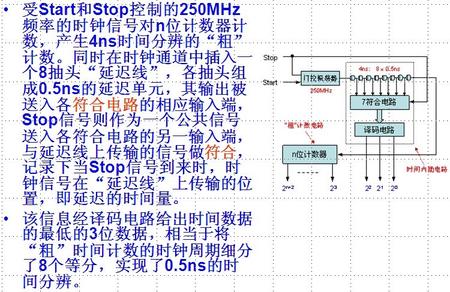

3、基于时间内插技术(Time Interpolating)的TDC

图3-1

图3-2

图3-3

图3-4

图3-5

图3-6

图3-7

4、基于时间邮戳(Time Stamp)技术的TDC

图4

•欧洲粒子物理实验室推出的通用性极强的高集成度TDC芯片HPTDC基于时间邮戳技术的TDC,时间精度为~25ps 。

•ACAM公司的GPX和GP2是基于时间邮戳技术的TDC商业产品。时间精度也在几十ps。

5、基于时间放大技术的TDC

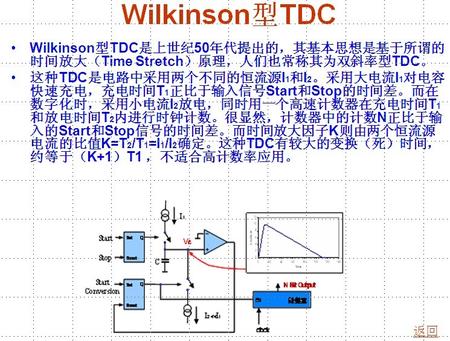

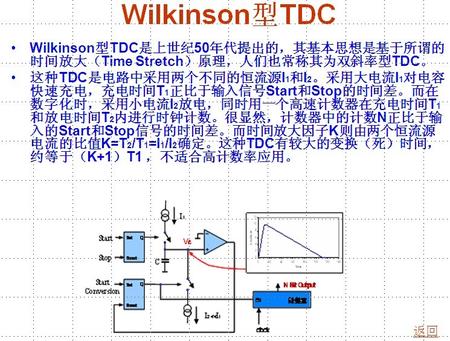

1)、型TDC

图5-1

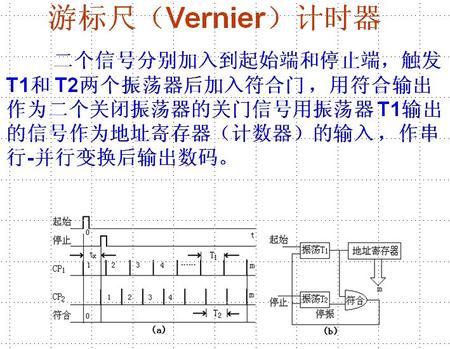

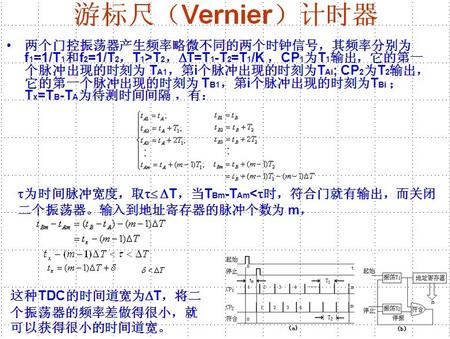

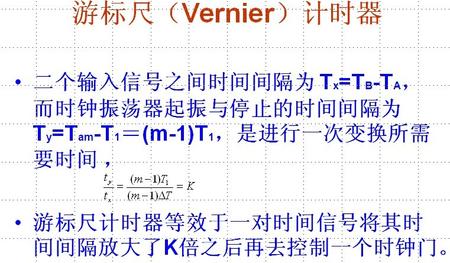

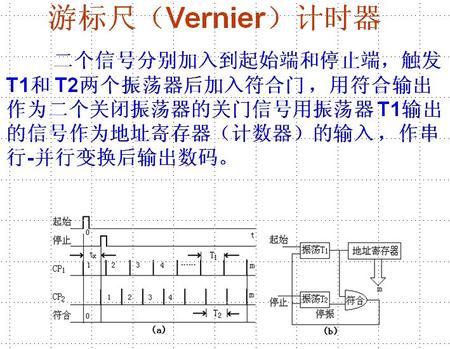

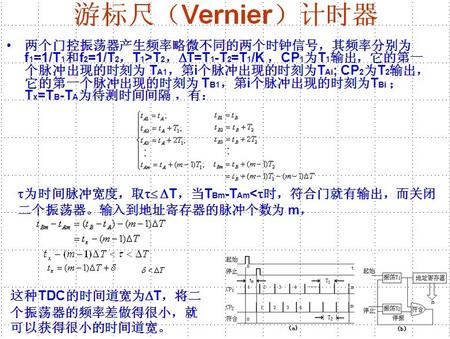

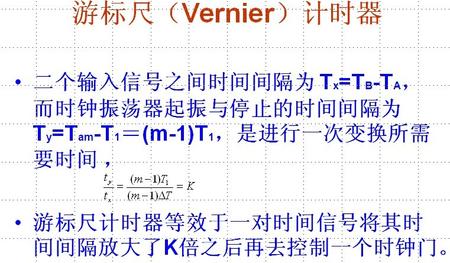

2)游标尺(Vernier)计时器

图5-2-1

图5-2-2

图5-2-3

/2

/2

用户377235 2015-6-16 11:13

coyoo 2013-1-14 09:22

用户242029 2013-1-11 15:23