概述

说明(三)探讨的是比较器一般带有滞回(Hysteresis)功能,为了解决输入信号转换速率不够的问题。前文还提到,即便使能滞回(Hysteresis)功能,还是无法解决SiPM读出测试系统需要解决的问题。本文在说明(三)的基础上,继续探讨为SiPM读出测试系统寻求合适的模拟脉冲检出方案。

前四代SiPM使用的高速比较器指标缺陷

由于前端模拟信号属于典型的指数脉冲,所以下降沿转换速率(Slew Rate)过慢,导致比较器检出出现不必要的问题。尽管比较器可以使能滞回(Hysteresis)模块功能,解决下降沿检出问题,但是使能滞回(Hysteresis)后,无法确保比较器参考阈值电平设置到足够低的水平,这样导致测试系统无法获取足够好的CTR结果。

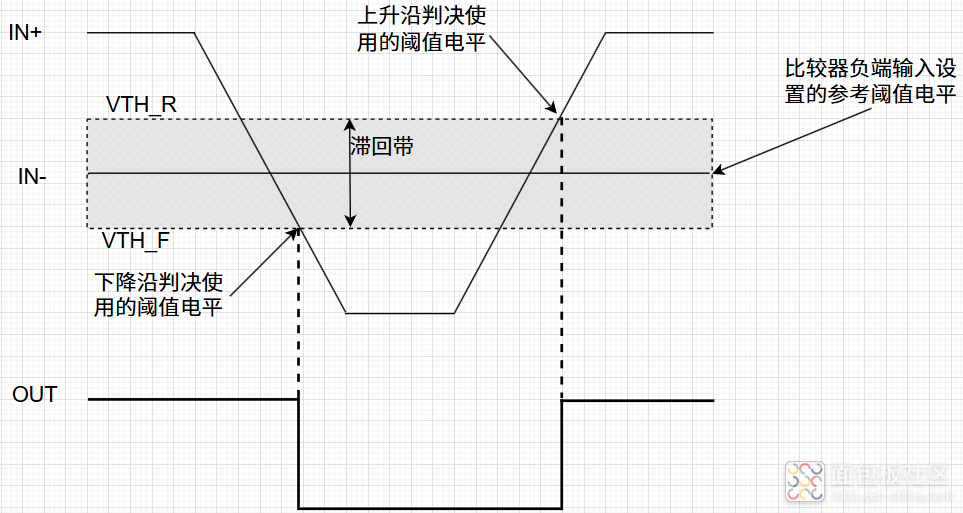

而导致上述参考阈值电压设置问题的原因,就是MAX9601EUP器件的迟滞范围过大。借着说明(三)中的迟滞示意图,如图1,图中中间“滞回带”(实际应用中需要尽可能减小“滞回带”),对于MAX9601EUP来说最小只能配置到5mV左右。

图1:迟滞工作原理示意图

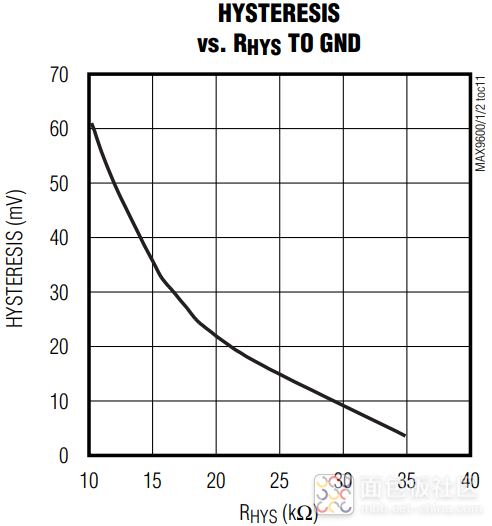

如图2所示,MAX9601EUP器件手册给出了该器件其迟滞参数可配置的范围,大致是从60mV到5mV左右。也就是为何在说明(三)中给出了,实际测试的时候,在开通迟滞功能后,比较器的参考阈值电压,最小只能设置到7mV,在6mV的时候,比较器输出就会丢失所有输入脉冲信号。所以,开通迟滞虽然可以解决让人头疼的比较器输出下降沿“台阶”和震荡问题,但是却带来另外的问题,即参考阈值电平设置受到了迟滞范围的影响。

图2:迟滞参数配置范围

除了上述指标缺陷外,在选择比较器的时候,还有一个容易忽视的指标,即输入偏移电压指标(input offset voltage)。MAX9601EUP的该指标在稳定室温情况下,最差是正负5mV,而在完整的工作温度范围内,该指标最差值是正负9mV。所以该指标也是导致系统CTR测量结果不理想原因。

总结

所以SiPM读出测试系统第四次迭代的结果,对于时间之路的研究并未得到理想的结果,需要更进一步迭代。需要选择更佳合适的比较器来替换当前使用的MAX9601EUP,目标选择的主要指标要求除了最初选择MAX9601EUP的要求外,着重关注滞回(Hysteresis)功能和输入偏移电压指标。比如,Hysteresis参数可以设置低至1mV左右,输入偏移电压最大值不超过1mV等。

参考

[1] Development of Multi-Channel Fast SiPM Readout Electronics for Clinical TOF PET Detector

[2] MAXIM, Dual ECL and Dual/Quad PECL, 500ps, Ultra-High-Speed Comparators

作者: coyoo, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1010859.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

Jun2024 2024-12-10 00:00

开发工匠 2024-12-5 11:49