概述

同一组前端模拟信号接入由不同型号ADC组成的模数转换电路时,采样后在FPGA中发现采样用时差异较大。本文主要分析这个时间差异形成的原因,并记录该差异产生对系统造成的影响。

系统数字化简介

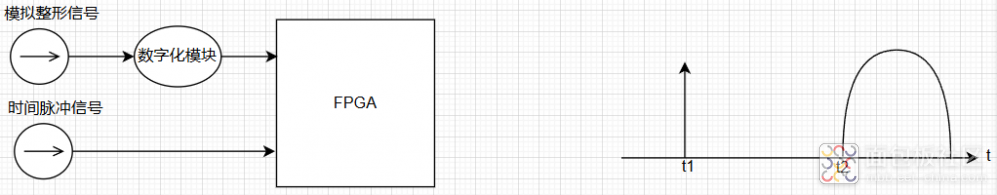

项目前端的模拟信号是由PMT或者SiPM加上LYSO探测器产生的整形脉冲波,同时随路产生时间脉冲,这个两个脉冲到达数字化板的时间保持不变,所以可以以时间脉冲为参考检测数字化后的整形模拟脉冲。即数字化脉冲上升沿触发后,固定周期后就可以得到对应的整形脉冲位置。如图1所示,在逻辑上,t1与t2之间的时间间隔在硬件确定后,即已确定,宏观上的差异不会存在纳秒级以上。

图1:模拟信号数字化框图及逻辑时序关系

数字化转换时差展示

这里需要首先明确一个前提,即大转换时差仅存在于AD采样电路中使用了不同型号的ADC。如果使用相同的AD采样电路,虽然存在采样时差,但是差异很小,这时候讨论的不是宏观的时差,而应该是通道之间的skew。

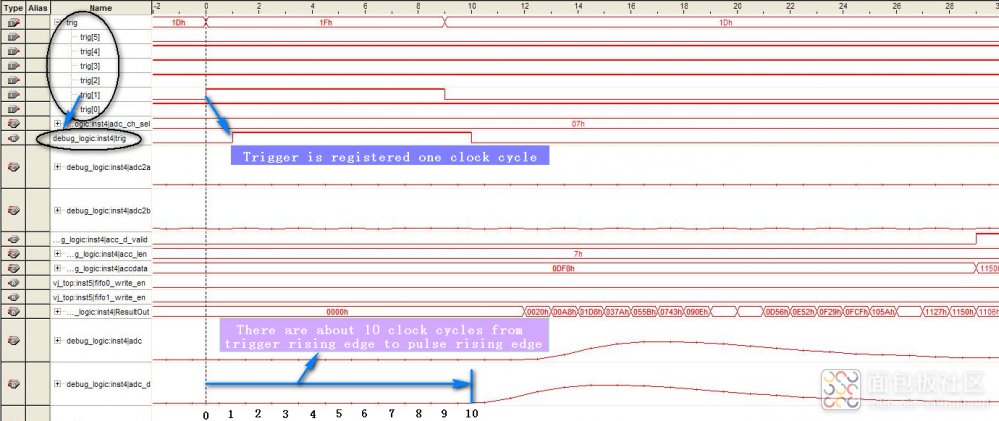

另外,本系统早期使用了AD9288 ADC,中期修改为AD9218,当前升级为AD9633。这里比较的是AD9218与AD9633之间的转换时间差异。如图2所示,即为早期AD9218采集PMT整形脉冲的实际时序关系。

图2:AD9218采集PMT产生的整形脉冲结果

如图2所示,SignalTapII的触发脉冲是时间脉冲信号,时间脉冲触动后,大概10个系统时钟后,整形脉冲被数字化完成并送到了FPGA。SiPM系统的时间关系大致如此,这个时间关系与硬件电路上的布线延时以及线缆连接造成的延时关系不大,因为这里关注的是基于系统时钟(100MHz)周期上的差异。硬件布线、连接等造成的延时基本上达不到时钟周期级别,故可忽略。图3则展示了AD9633采集SiPM后得到的时间脉冲与整形之间的时序关系。

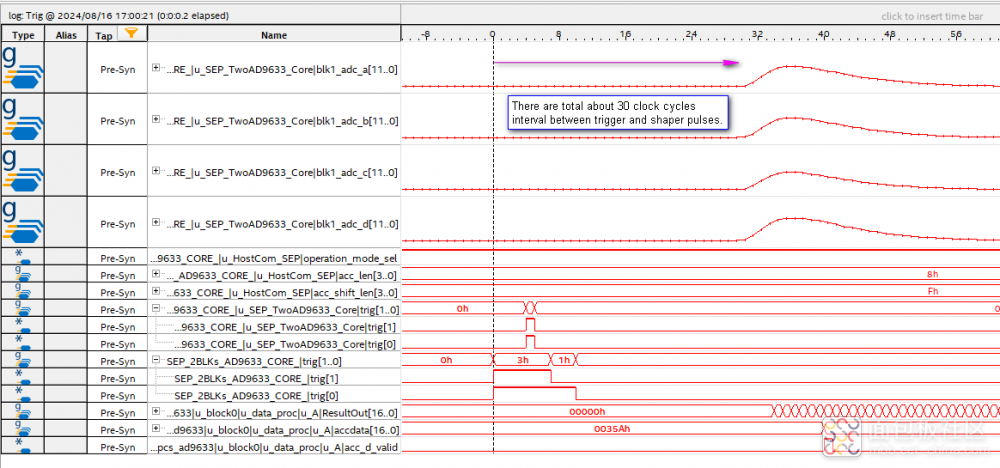

图3:AD9633采集SiPM产生的整形脉冲结果

如上图所示及之前分析,PMT与SiPM硬件电路上产生的时间脉冲与整形脉冲之间时间间隔差异并不大,这个也使用AD9218采样后验证过。而上图使用AD9633采集后得到的这个时间间隔在30个时钟周期,大于图2中的10个时钟周期,差异在20个时钟周期。

数字化转换时差原因分析

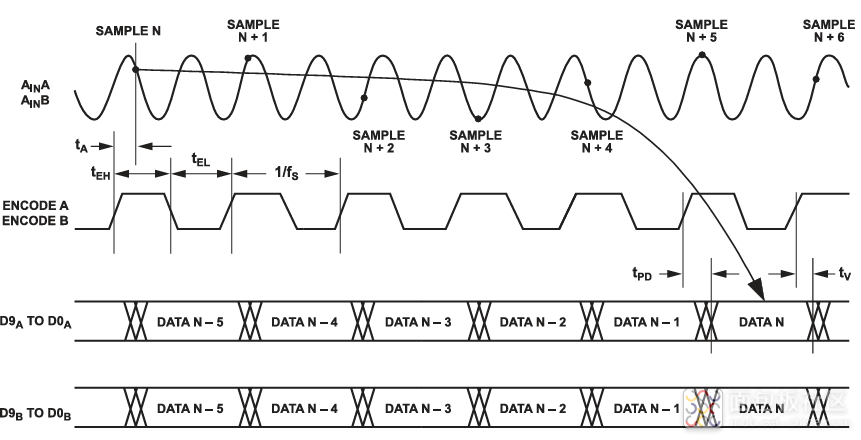

通过查看两个ADC的数据手册,发现在流水延迟这个参数上,二者有着很大的不同。AD9218给出的数字输出流水延迟是5个时钟周期,如图3所示中箭头所指。

图3:AD9218正常工作的通道时序

而同样的参数,AD9633给出的是16个时钟周期,所以这里的差异在11个时钟周期。但是,还有9个左右的时钟差异在哪儿呢?

剩下的9个时钟差异应该来自于FPGA内部,因为AD9218是并行输出,FPGA直接获取AD的输出数字码,而AD9633是LVDS串行输出,FPGA收到后首先需要进行解串,解串LVDS逻辑模块运行周期目前还不明确,需要查看资料确认。

参考

作者: coyoo, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1010859.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/2

/2

文章评论(0条评论)

登录后参与讨论