TimeQuest之multicycle paths

王敏志

概述

Multicycle paths即多周期路径,指的是两个寄存器之间数据要经过多个时钟才能稳定的路径,一般出现于组合逻辑较大的那些路径。在实际工程中,除了乘除法器等少数比较特殊的电路,一般应该尽量避免采用多周期路径电路。即使有所使用,也应该通过约束在综合工具中指出该路径,使得综合工具在计算Fmax的时候忽略这条路径,避免用大量的时间对该路径进行优化。 对多周期路径可加一下约束:set_multicycle_path -from D_reg -to S_reg。

本文成文之前参考了网上《DC概论之多周期路径》,并使用其中一些例子,这里对作者的辛勤劳作表示感谢。《DC概论之多周期路径》网上链接众多,本人不负责辨认何处为原创,这里只是给出其中一个链接:

http://bbs.ednchina.com/BLOG_ARTICLE_214699.HTM

另外,这里有一个疑似原创出处:http://www.cnblogs.com/liuokay/category/291986.html

关于何时何处使用Multicycle Path

上述《概论》论述的是IC设计的时候的多周期路径,那么对于FPGA设计特别是ALTERA的FPGA设计的时候何时何处会用到多周期约束呢?其实简单点说就是设计者如何知道自己的设计中哪里需要进行多周期设计的问题。

在设计中很多地方都有涉及多周期路径,当个两个触发器之间的逻辑如果一个周期执行不完的话一般有两个解决方案:

1、插入流水线使得组合逻辑打散 ;

2、使用使能信号控制,几个周期读取一次数据。

这里面2所使用的方法就需要设定multi-cycle path,方法2和1之间是有区别的。方法1数据的吞吐量更大,方法2牺牲了数据吞吐量,但是设计中有的地方对吞吐量没有要求是可以使用这种方法的。

举个简单的例子,某个设计大部分逻辑可以跑1G,但有个乘法器只能跑100M, 所以你就把multi-cycle设成10T, 但是design也要修改, 就是每10T才采集一次乘法器的结果。

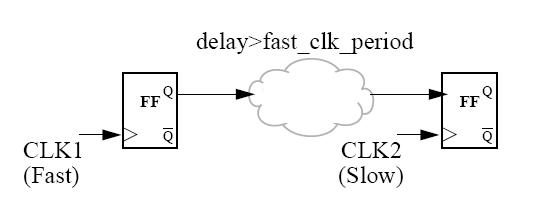

在《概论》里详细介绍了所谓的“快采慢”和“慢采快”的两种情况,可以很好理解两个不同寄存器的采样时钟频率不一样时的情形。

多周期的分类

这里有必要交待一下多周期的分类,说到这个分类,有两种。一种就是上述《概论》里提到的快采慢和慢采快,另外一种是Setup多周期和Hold多周期。

ALTERA其实对于第一种分类是这样描述的,即分为Destination和Source。Destination是基于目标时钟沿,向后移动Latch时钟沿来放松建立保持时间。而Source约束是基于源时钟沿,通过向前移动Launch时钟沿来放松建立保持时间。Start和end说明多周期路径依赖于start clock还是依赖于end clock。

ALTERA关于第二种分法的描述是这样的,即Setup多周期是增加建立时间分析的周期数,默认情况下是1个周期。Hold多周期是增加保持时间分析周期数,默认情况下是0。Setup和Hold说明多周期路径是用在建立时间检查还是用在保持时间检查。

具体什么是多周期路径约束呢?

时序分析器会分析除了定义为false path的所有路径。所有的路径都是在最近的沿分析setup,在最近的沿的前一个沿分析hold。 设置为multicycle 的path会改变分析方法, 比如muticycle 2就是说会在最近的沿的下一个沿分析setup,分析setup的沿的前一个沿分析hold。

具体的多周期路径约束语法如下所示:

set_multicycle_path [-h | -help] [-long_help] [-end] [-fall_from <names>] [-fall_to <names>] [-from <names>] [-hold] [-rise_from <names>] [-rise_to <names>] [-setup] [-start] [-through <names>] [-to <names>] <value>

-start:选择源(source)多周期

-end:选择目标(destination)多周期(默认)

-setup|hold:指定建立或者保持多周期

<value>:扩展分析的周期数目

其他基本和false path命令基本相同。下面通过几个例子来具体说明如何理解多周期。

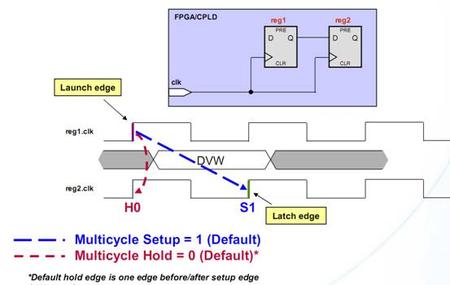

1、 标准单周期寄存器传输

图1

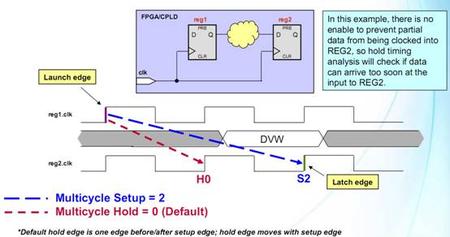

2、 双周期setup,单周期hold传输

图2

那么图2所示的多周期路径约束如下所示:

Set_multicycle_path –from [get_pins reg1|clk] –to [get_pins reg2|datain] –end –setup 2

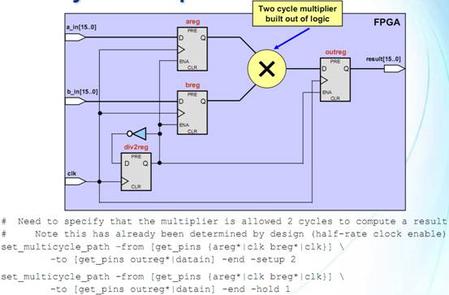

3、 实际应用中经常遇到的乘法器多周期例子

图3

前面有介绍,在多周期设置中,Setup的周期是X,那么设置的Hold周期为X-1。所谓的快采慢如图4所示,请注意《概论》中的默认情况和ALTERA的TQ工具里默认情况的异同。概论里提到的工具如果命令没有指明Start和end,那么默认情况下Setup是参照end,而Hold参照start。而ALTERA似乎均默认为end。

图4

假设已经知道3*clk1>delay>2*clk1,这时候多周期约束为

set_multicycle_path -setup 3 -end -from clk1 -to clk2

set_multicycle_path -hold 2 -end -from clk1 -to clk2

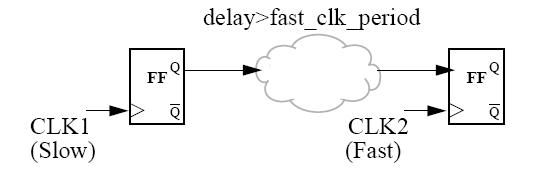

再来看看“慢采快”,如图5所示

图5

假设已经知道3*clk1>delay>2*clk1,这时候多周期约束为

set_multicycle_path -setup 3 -start -from clk1 -to clk2

set_multicycle_path -hold 2 -start -from clk1 -to clk2

最后再来一个“慢采快”的例子,100MHz时钟分频得到一个50MHz的时钟,那么为从100MHz到50MHz时钟域所有路径加一个源多周期为2,保持多周期为1的约束如下所示:

create_clock -period 10.000 -name CLK [get_ports clk]create_generated_clock -divide_by 2 -source [get_ports clk] -name CLKDIV2 [get_registers clkdiv]set_multicycle_path -start -setup -from [get_clocks CLK] -to [get_clocks CLKDIV2] 2set_multicycle_path -start -hold -from [get_clocks CLK] -to [get_clocks CLKDIV2] 1 /2

/2

文章评论(0条评论)

登录后参与讨论