ECO那些事之LE与ALM

王敏志

概述

这里继续《ECO那些事之属性编辑器》一文,描述下如何在属性编辑器里对LE以及ALM进行手动修改。重点比较一下LE与ALM在属性编辑器中的区别,通过这些比较就可以很容易地理解为何在ALTERA的高端FPGA中实现TDC功能的难度要比其低端器件高很多。

在《基于FPGA的TDC那些事之设计资源LAB》一文中对于ALTERA高低端器件组成LAB不同的单元LE和ALM进行了介绍,同时也作了比较。本文笔者希望站在ECO处理角度再次进行比较介绍LE和ALM。

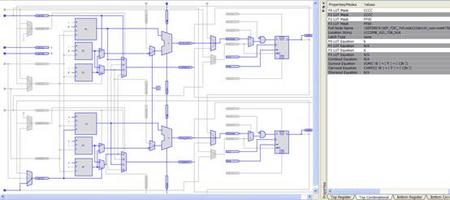

LE在属性编辑器中概览

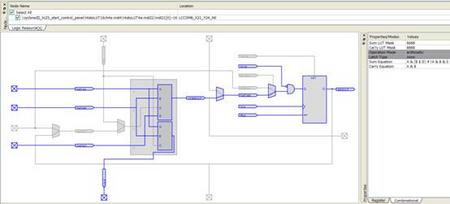

在《ECO那些事之属性编辑器》一文中,有一节详细描述了LE的属性,由于笔者主要使用ECO修改TDC设计,所以这里重点关注LE的算术模式。在算术模式下,LUT可以理解为两个三输入子LUT。第一个三输入子LUT产生相加“和”信号输出,第二个子LUT用于产生进位输出信号。当LE配置为算术模式时,用户不仅能更改SUM方程式,还可以修改CARRY进位方程式。如图1所示,右侧的SUM等式和Carry等式都是可修改的,当然也可以通过修改SUM和Carry LUT掩码来自动更新等式。

从图1可以看出,虽然LUT分成了两个子LUT但是求和输出(Sumout)只与LUT(注意与LE的区别)的输入有关,这个从图左侧的视图或者右侧的SUM等式都可以清楚看到。这点是LE与ALM最大的区别,后面详述。

图1:配置成算术模式LE属性编辑器概览

另外,注意图1右侧等式里的符号“#”和“$”,在《ECO那些事之属性编辑器》一文中已经对其所代表的涵义进行了推导,理解其含义对于利用ECO修改LE和ALM很重要。为了便于比较,图2给出的是当LE配置为Normal模式下时,其属性编辑器的概览。可以看到,左侧只有一个LUT,而右侧的Carry掩码以及Carry等式均为“N/A”状态。

图2:配置成Normal模式LE属性编辑器概览

ALM在属性编辑器中概览

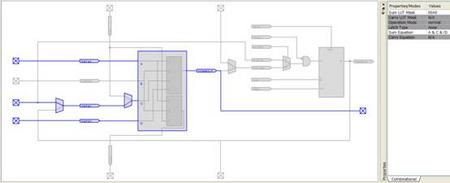

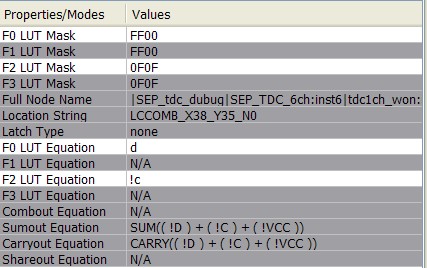

ALTERA的宣传资料在介绍ALM的时候通常如《基于FPGA的TDC那些事之设计资源LAB》一文中图3那样进行简单介绍。ALM的工作模式比LE多出了几个,其实主要模式还是Normal和算术模式。图3所示为ALM的Normal模式。

图3:Normal模式下的ALM

如果只看图3,似乎和图2的LE没什么太大区别(多个LUT,及LUT的输入更多),其实除了图3表面的这些区别之外,如果深入到属性编辑器可以发现更多细节的不同处,如图4所示。

图4:配置在Normal模式下ALM属性编辑器概览

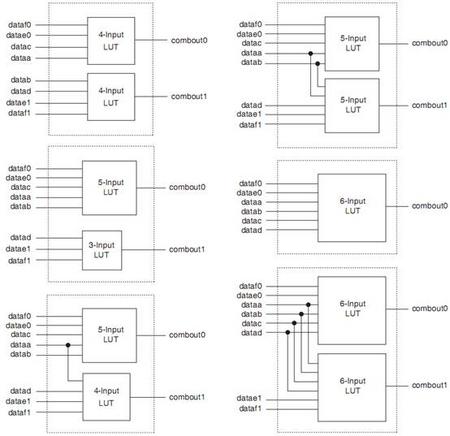

虽然Normal模式不是本文的重点,但是这里还是有必要比较并列举出图2和图4的主要差别点,有些差异在算术模式下一样。

l ALM包含2个ALUT,所以属性栏分别包含TOP和BOTTOM两栏

l ALM的属性编辑器里属性栏没有显示当前察看的ALM的工作模式

l 每个ALUT被分为3个子LUT,上面的分别为1个F0 LUT和2个F0 LUT,下面分别为1个F1 LUT和2个F3 LUT

l ALM内包含有2个加法器,不象图1中的LE需要LUT自己实现加法功能

l 多出端口DATAF、DATAE,以及这两个端口和其它端口在ALM内部路径是有区别的

l 端口DATAD也和LE有些许区别

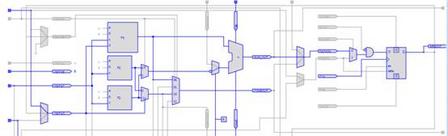

上面列举的这些差异,都是造成ALTERA高端FPGA器件中实现TDC功能难度增大的原因。那么,逻辑实现TDC功能,还是需要利用逻辑单元的算术模式,其在属性编辑器中概览如图5所示。

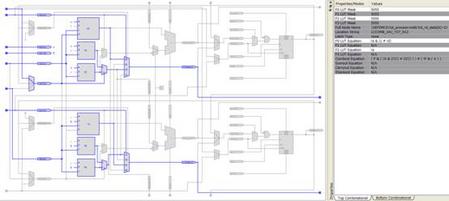

图5:配置在算术模式下ALM属性编辑器概览

比较图4和图5,明显区别是ALM中的加法器以及寄存器都被利用起来了,而且右侧的属性栏里多了有关register的两项。

利用属性编辑器手动修改ALM

在《ECO那些事之属性编辑器》一文里也举了几个利用属性编辑器简单的修改ALM例子,特别是在推导符号“#”和“$”功能的时候。笔者这里首先给出的一个例子是对《ALTERA FPGA/CPLD设计 – 基础篇》中关于属性编辑器一段描述的存疑。在该书的第179页的表5-1中列出了LUT掩码真值表。图6给我们展示了实际输入DATAD和DATAC的真值,即分别为“FF00”和“F0F0”,那么DATAA和DATAB的真值也很容易知道,这和该书籍上的描述不一致,该书将ABCD正好弄反了。

图6:LUT输入真值

接下来,我们注意虽然ALM有8个输入,但是每个子LUT的方程式只能包含A、B、C和D,不能包含F0 、F1、E0和 E1,而Sumout方程式和Carryout方程式中可以包含,而我们知道这两个方程式不能直接进行修改。

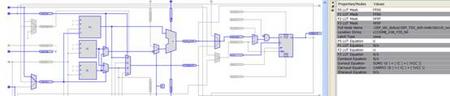

图7:修改前ALM上半部分

图7是图6对应的ALM原理视图,三个子LUT的输入只有DATAC和DATAD,这和图6中的求和及进位方程式相符。如果我们要把DATAC移到DATAF,会发生什么呢?如图8所示,我们发现这时候QuartusII并没有自动更新LUT掩码以及方程式。这时候如果使用ECOs得到的结果是不对的,因为方程式中使用的DATAC根本没有任何连接。所以还需要手动修改LUT方程式,使得Sumout方程式由SUM((!D)+(!C))+(!VCC)变成SUM((!D)+(!F))+(!VCC),同样的Carryout方程式也会得到自动更新。注意这里的目的不是要改变逻辑功能,只是简单将DATAC上的信号移到DATAF(这点在以后的TDC设计中非常重要,因为我们不是要改变功能,而是要改变路径,即信号path)。

图8:只是将DATAC移动到DATAF

那么应该修改那个子LUT方程式呢,分析图8,应该是修改F2子LUT方程式,但是怎么修改呢,经过尝试,发现修改方程式到“!d”即可,如图9所示,修改F2子LUT方程式导致其他方程式及掩码得到了自动更新。至于为何是“!d”还未搞清楚,反正是跟DATAD有关系。

图9:修改子LUT方程式并自动更新求和及进位方程式

上面这个例子充分回答了之前笔者所说的上述ALM与LE的差异会如何导致实现TDC功能难度的增加,同时这个例子也揭示了我们应该如何在高端FPGA中正确的进行TDC设计。

分析及结论

本文在属性编辑器的角度进一步比较了LE和ALM的异同,给普通客户揭开了一个小缝隙,使其可以了解ALTERA的编译工具是如何对逻辑单元进行布局布线的。学习ECO修改设计,从而确保TDC在高端FPGA器件成功实现。

/5

/5

文章评论(0条评论)

登录后参与讨论