ECO那些事之属性编辑器

王敏志

概述

进行ECOs有两种方法,一种是直接在Chip Planner里进行,另外一种是在属性编辑器里进行ECOs。本文试图结合笔者在TDC设计中使用的功能尽量详细地描述一下属性编辑器,毕竟属性编辑器可以编辑的属性较多,笔者并未对每一种属性进行过编辑,只是给出三两个例子希望能抛砖引玉。

什么属性编辑器?

在文章《基于FPGA的TDC设计那些事之利用ECOs手动修改设计》和《PLL那些事之core输出抖动》都有涉及ECOs,且都是通过属性编辑器来完成的。那么什么是属性编辑器呢,属性编辑器即Resource Properties Editor,QuartusII在工程的任何地方都可以通过“locate”命令进入属性编辑器,当我进行ECOs时,我习惯先打开Chip Planner再通过双击其中需要编辑的单元进入属性编辑器,因为ECOs最终还是需要在Chip Planner中完成。

在属性编辑器里可以编辑的单元有LE、ALM、PLL、I/O Element、RAM以及DSP模块。在进行TDC设计的时候我们仅需要修改LE或者ALM和PLL,所以本文只以这两者为例来详细说明如何使用属性编辑器。

逻辑单元(LE)的属性

通过翻阅QuartusII手册的第17章,可以查到本节的详细介绍,手册详细介绍了LE而简单介绍了ALM属性,这里按照手册的内容尽量详细描述,另外试图比较LE和ALM属性的异同。下面先介绍LE可修改的属性。

1、 工作模式

逻辑单元LE可以工作在正常模式和算术模式两种模式。当LE配置工作在正常模式时,四输入查找表LUT能实现四输入变量的所有功能。当LE配置工作在算术模式时,LUT可以理解为两个三输入子LUT。第一个三输入子LUT产生相加“和”信号输出,第二个子LUT用于产生进位输出信号,该信号仅仅能驱动另一个LE的进位输入信号。

2、 LUT方程式(EQUATION)

用户可以通过修改逻辑方程式而更改当前LUT实现的功能。当LE配置为正常模式时,用户仅仅能修改SUM加法方程式。当LE配置为算术模式时,用户不仅能更改SUM方程式,还可以修改CARRY进位方程式。

当LUT方程式被更改了后,QuartusII软件就自动更改了LUT的掩码。

为了更改由LUT实现的功能,首先用户必须了解LUT如何工作。一个LUT实际上是由内部的存储单元来实现逻辑功能的,而这个逻辑功能是其输入变量的函数。每一个存储单元能保存一个逻辑值,0或1。ALTERA比较老的器件族最小逻辑单元是LE,里面的四输入LUT有16个存储单元。LUT在其存储单元中保存了16个输出值,而LUT的输出又由此LUT的驱动输入端口的信号所决定。

3、 LUT掩码(MASK)

LUT实现什么功能、输出什么值都是由LUT掩码决定的。为了产生LUT掩码,必须算出要实现功能的方程式的真值表。

当LUT掩码改变了以后,QuartusII软件将自动更新LUT方程式,反之亦然。表1是LUT掩码真值表,表的最后一列输出要根据不同的LUT方程式才能得到,后面我会给出几个例子来说明。

表1:LUT掩码真值表(由上到下依次从LSB –> MSB)

4、 同步模式

每个LE的寄存器都包含同步加载(sload)和同步清除(sclr)信号。用户可以将它们进行取反修改。如果某个LE使用了sload或者它的取反值,那么该LE所在的LAB里所有LE只能使用此sload及其取反值。例如某个LAB里的两个LE用到sload,那么这两个LE的sload值必须一样。同样规则也适用于sclr。

5、 寄存器级联模式

如果用户使能了寄存器级联模式,那么Cascade-in端口连到寄存器的数据输入端。寄存器级联模式大部分是用于设计需要实现一系列移位寄存器的时候。用户可以通过更改Cascade-in端口的连接或不连接而更改寄存器级联模式。如果用户需要产生这个端口,那么源端寄存器必须在目的端寄存器的正上方,这样才可以级联起来。

6、 单元延时表

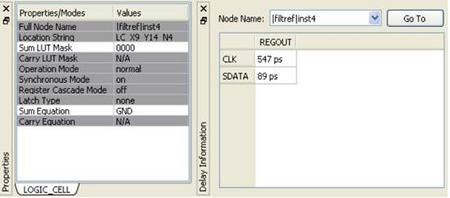

单元延时表(Cell Delay Table)描述了从LE的输入到输出的传输延时。图1是从QII12.1的手册里摘录下来的图示,不知道这是否是Cell Delay Table,但是我实际使用的QII11.1用属性编辑器查看LE的属性时候并没有看到所谓的单元延时表。如果能查看到这个属性,对于TDC的设计参考意义还是非常大的,可惜本人并没有找到。笔者获得类似图1所示的延时信息,是通过TimeQuest才察看到的,后面我会给出例子。

图1:逻辑延时信息

PLL的属性

属性编辑器允许用户修改PLL的配置参数,例如输出时钟的相移、占空比等等,下面所列都是可以更改的属性。

l 输入频率

l M VCO tap

l M初始值

l M值

l N值

l M计数器延时

l N计数器延时

l M2值

l N2值

l SS计数器

l Charge pump current

l 环路滤波器阻抗(Loop filter resistance)

l 环路滤波器容抗(Loop filtercapacitance)

l 计数器延时

l 计数器上限(Counter high)

l 计数器下限(Counter low)

l 计数器模式

l 计数器初始值

l VCO tap

1、调整占空比

利用下面公式可以单独为某个输出时钟调整占空比。

![]()

2、调整相移

利用下面公式可以单独为PLL的输出时钟调整相移。

Phase Shift = (Period VCO*0.125*Tap VCO) + (Initial VCO*Period VCO)

PLL工作在正常模式下时,Tap VCO ,Initial VCO,和Period VCO都由下列公式得到:

Tap VCO = Counter Delay – M Tap VCO

Initial VCO = Counter Initial- M Initial

Period VCO = In Clock Period * N + M

当PLL工作在外部反馈模式的时候,Tap VCO ,Initial VCO,和Period VCO都由下列公式得到:

Tap VCO = Counter Delay – M Tap VCO

Initial VCO = Counter Initial- M Initial

Period VCO = ![]()

当然还有通过其它公式去修改PLL的输出时钟的频率,以及频谱扩展等等,这里不一一描述,详细可以查看QuartusII手册,对于TDC设计最重要的是要调整时钟的相移,在文章开始提到的文章中就有此应用。

属性编辑器应用举例

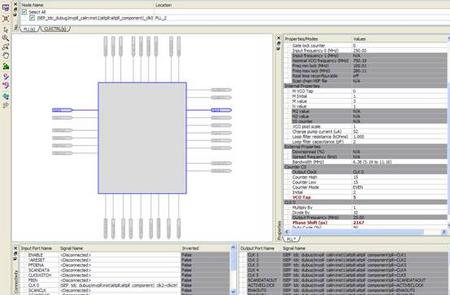

首先我们举一个通过属性编辑器修改PLL的属性的例子,根据上述调整相移的部分,我们知道通过修改对应输出时钟的VCO Tap或者Counter Initial来修改此时钟的相移,如图2所示。

图2:利用ECO手动修改PLL输出的相位

这个例子在TDC设计中的应用,主要是在没有Random HITs之前利用PLL的输出来测试TDC的性能。通过属性编辑器,我们可以通过皮秒级别的相移完全可以达到测试TDC的目的。另外,设计调试过程中发现在测试ADC的时候也可以用得到,由于ADC的采样时钟和FPGA的系统时钟异步,所以FPGA采集ADC输出数字信号可能没有对齐其安全窗口,从而导致数据错误,可以通过属性编辑器逐步调整时钟的相位找到合适采样窗口,这个SDRAM有点类似。

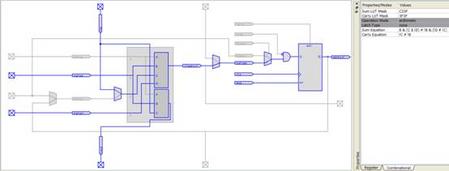

下面回到本文的重点,即通过属性编辑器来对LE或ALM的属性进行编辑。图3是CycloneIII里某个LE,Carry方程式是“!C#!B”,Carry LUT掩码为“3F3F”。那么根据表1可以得出符合“#”是逻辑或。

图3:LUT方程式和掩码

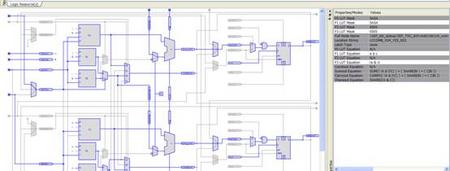

图3是为我搞清楚#在ALTERA的属性编辑器到底表示什么逻辑功能,最新的所有资料上我都没有查到,也许以前老版本的QII手册上有,可惜找不到了。如果不搞清楚这些符号的功能,根本看不懂方程式。类似的符合还有一个“美刀”符合 - $,继续找找例子反推(图3中有符号$,但是方程式太复杂很难推导)。找个简单点的方程式,如图4所示是在ArriaGX的某个ALM中的方程式和掩码。

图4:推导异或符合

图4中F1 LUT方程式是“a$c”,而其掩码是“5A5A”,根据表1可以推导符号$是逻辑异或符号。

只有搞清楚上述ALTERA专用的逻辑符号,才能放心去修改掩码或者方程式。在TDC设计中,一般只需要修改LE或者ALM的数据输入端口,需要注意的是,这些修改会导致QuartusII自动更新掩码或者方程式,需要确认更新后的内容是否符合设计需求。例如,TDC设计如果将数据端口DATAA的信号更改到DATAF,这时候虽然方程式虽然自动更新,但是它自动更新的是DATAA端口信号到方程式里,而实际我们需要使用的是端口DATAF上的信号,所有还需要更改方程式。文章《基于FPGA的TDC设计那些事之利用ECOs手动修改设计》给出了一个例子,即外部HIT从ALM不同的数据端口输入到ALM输出的延时有很大差异。

分析及结论

本文详细介绍了什么属性编辑器,如何在属性编辑器中进行ECOs。介绍了LE以及PLL的可编辑属性。通过实例推导了ALTERA的QuartusII中表示逻辑或和逻辑异或地专用符号。

/3

/3

用户1867027 2016-2-25 11:08

coyoo 2016-2-25 10:36

用户1867027 2016-2-25 10:06

royalark_912907664 2013-4-3 13:05