基于FPGA的TDC那些事之精度

王敏志

概述

TDC的精度是我们设计TDC时最关注的因素,那么如何衡量基于FPGA的TDC的精度呢。一直以来使用FPGA来设计TDC进展缓慢,就是无法解决精度提高的问题,精度受限于逻辑单元的延时时间。本文试图剖析全新的基于FPGA的TDC设计方法在提高TDC测量精度方面的探索。

TDC之Raw BIN

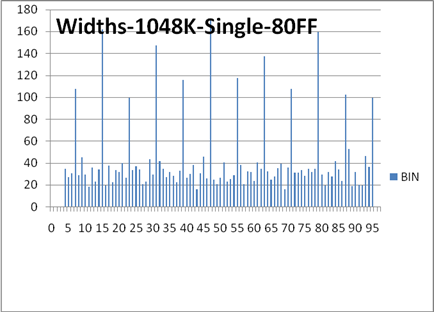

FPGA逻辑实现的Delay Line延时单元的延时时间收敛性不是特别理想,图1是实际测量的结果,延时链上延时单元的延时时间变动范围从十几皮秒到一百七十几皮秒,但还是比传统直接使用逻辑资源来产生延时要小得多,而且一致性也好很多。

图1:TDC的Raw Bin

图1显示了延时链BIN具有不均匀性特点,这是一个很大的缺点,但是如果加以利用就可以将这些不均匀的Bin进行相互切割,从而达到平滑的目的。

对TDC的Raw BIN进行平滑

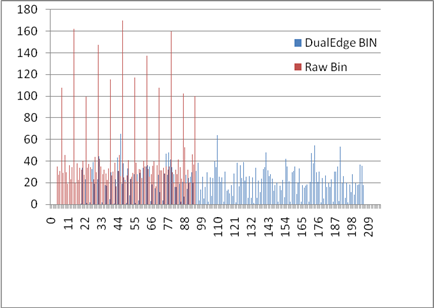

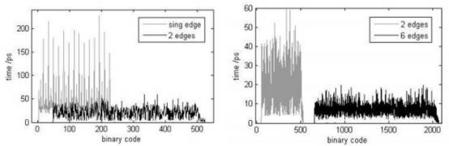

上一节谈到了可以利用Raw BIN的不均匀性来对BIN进行切割,实际经过切割后的TDC的Bin如图2所示。经过切割后的BIN平均值在20ps左右,而最大的BIN也只有65ps左右,远远小于Raw BIN的最大值170ps。图3显示的是在公开发表的文章上有人已经做过的多沿切割后得到的BIN宽,可以看到6沿切割后,BIN平均值在10ps左右,而最大值也只是20ps左右。需要注意的是,多沿切割虽然提高了TDC的精度,但是同时带来死时间增加的缺点,所以实际应用的时候需要综合评估采取合适的切割方案。

图2:BIN宽

图3:公开发表的多次切割后BIN

再谈TDC自动校准

如果我们采用双沿切割,从图2可知,TDC的精度应该由BIN的最大值决定,即65ps左右。然而实际应用中,精度还跟温度以及FPGA的供电电压有关,所以需要对TDC的BIN进行实时地BIN-by-BIN校准。自动校准并不能提高TDC的测量精度,但是可以大大减小因温度、电压等因素造成的测量误差。

图4是由图2中的直方图合成的查找表,在具体操作过程中,会随时对直方图进行更新,达到某种条件时又能对LUT进行更新调整,所以称为实时半连续自动校准。

图4:校准查找表(LUT)

结论

阐述了基于FPGA的TDC精度如何超脱延时链延时单元的延时时间,理解BIN切割和自动校准分别对精度的影响。

/5

/5

luoyong422802_790352228 2016-3-25 11:01

tengjingshu_112148725 2009-4-13 09:23