基于FPGA的TDC那些事之自动校准

王敏志

概述

基于Delay Line的TDC精度都会随着温度电压的变化而变化,我们知道ACAM公司的TDC有一种模拟校准的方法,而基于FPGA的TDC无法利用模拟的方式来进行校准,必须采用数字方式来进行校准。

TDC之BIN

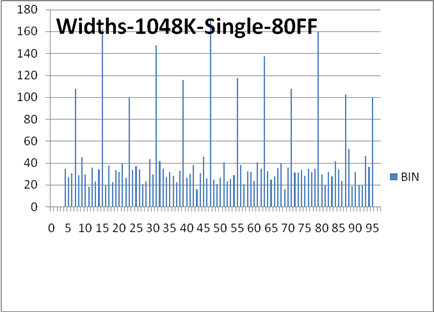

FPGA逻辑实现的Delay Line延时单元的延时时间收敛性不是特别理想,图1是实际测量的结果,延时线上延时单元的延时时间变动范围从十几皮秒到一百七十几皮秒,故需要进行校准。

图1

图1显示了延时线BIN具有很大DNL,并且如概述里描述的那样,上图中的BIN还会随着FPGA所处环境温度以及其供电电压的变化而变化,所以需要对BIN进行尽可能快速地校准,而且最好是实时在线地进行校准。

平均延时和BIN-by-BIN方式

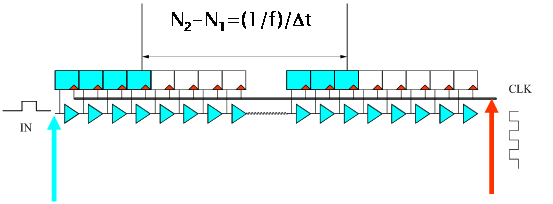

数字校准在FPGA中目前至少有两种实现方式,分别是平均延时和BIN-by-BIN方式。所谓的平均延时校准结构,简单点说就是获得图1中所有BINs的平均值,具体在FPGA中实现的方法展现在图2中。Delay Line总的延时时间长度被设计成大于一个时钟周期,所以某些HIT会被Delay Line“捕获”两次,那么两次“捕获”之间的时间间隔就正好等于一个时钟周期,而两次“捕获”之间延时单元的个数是可以知道的,即如图2中的N2-N1,那么N2-N1=Tck/τ,由此公式可以算出τ的数值,即延时单元的平均延时时间。

实际情况下,这个N2-N1不是一个固定值,甚至有时候应该要用小数来表示,所以实际设计中τ也应当是经过多次测量得到,这样也就提供更高精度的校准。

图2

平均延时校准方式的优点是系统反应时间快,可以快速的对TDC系统进行校准。前面提到了,τ只表示Delay Line的延时单元的平均延时时间,所以这种方式无法提供BIN by BIN的校准,特别是每一个BIN的宽带都不一样的时候。对于我们基于FPGA的TDC强烈推荐使用基于BIN-by-BIN的校准方式,因为FPGA TDC的BIN在一个很大范围内变动。

将TDC的BINs校准到BIN的中间位置

这其实是一个对齐的问题,所有的BIN经过校准以后,应该是以BIN的上限(某个BIN其实就是一个时间范围,所以这里有所谓的时间“上限”和“下限”的概念)对齐呢,还是以下限对齐呢,或者是以BIN的中间对齐呢?

我们假设所有BIN的宽度已经测量好,并且存在阵列ωk中。那么第n个BIN正对其中间校准好的时间tn的公式如下所示

![]() (1)

(1)

需要强调的是,第一个BIN的半个BIN宽度值不能被忽略掉。上面公式右边的求和其实就是将BIN校准到BIN的边沿,加上半个BIN宽度正好校准到BIN的中间位置。校准到BIN的中间位置的好处是因为这样做的时候测量的RMS误差是最小的,只有当所有延时单元的延时时间都一样的时候,校准到边沿或者中间效果是一样的。

实际逻辑校准就是合成LUT的过程,这个过程可以分为下面几个关键步骤

1. 第一个BIN的一半宽度成为其中间位置时间;

2. 第一个BIN的剩下的一半加上第二个BIN的一半组成了第二个BIN的中间位置时间;

3. 同样地方式获得剩下的BIN的中间位置时间。

下面给出了从DNL直方图数据中合成LUT的整个过程:

假定直方图中地址0中的数据为Q0,Q0’则为Integrate后更新到此地址的数据,也即Q0’为新LUT地址0的数据,依次类推。Dt0为Integrate地址0时外部累加器产生的中间结果(其实就是在HCNT=7时累加器结果,当前写入LUT中的值是直方图的输出加上上一个地址Integrating时HCNT=7时累加器结果)以备地址1 Integrating时所需,以此类推。那么下面分解整个Integrating的过程:

Q0 + 0 = Q0’; Q0’ + Q0 = Dt0

Q1 + Dt0 = Q1’; Q1’ + Q1 = Dt1

Q2 + Dt1 = Q2’; Q2’ + Q2 = Dt2

…………………………………………

Qn-1 + Dtn-2 = Qn-1’; Qn-1’ + Qn-1 = Dtn-1

Qn + Dtn-1 = Qn’; Qn’ + Qn-1 = Dtn

那么,我们来看Qn’到底等于多少呢,也即LUT中某个地址中的数值

Qn’ = Qn + Dtn-1= Qn + Qn-1’ + Qn-1 = Qn + 2Qn-1 +Dtn-2

= Qn + 2*Qn-1 + 2*Qn-2 + … + Q3 + Q3’

= Qn + 2*Qn-1 + 2*Qn-2 + … + 2*Q3 + Q2 + Q2’

= Qn + 2*Qn-1 + 2*Qn-2 + … + 2*Q3 + 2*Q2 + 2*Q1 + 2*Q0

所以

Qn’ = Qn + 2*![]() Qk。 (2)

Qk。 (2)

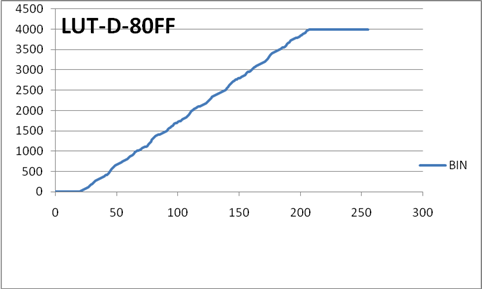

注意公式(2)和公式(1)其实没有分别。经过校准后的获得了很好的效果,如图3所示。

图3

结论

本文主要是阐述了在FPGA实现数字校准的原因,分析了数字校准的方法,推导了数字校准的过程。

lifengyu 2021-7-14 15:07

coyoo 2014-12-25 08:31

用户1475633 2014-12-24 13:35

coyoo 2014-12-24 09:00

用户1475633 2014-12-23 16:24