SignalTap II应用小实例之触发位置

概述

SignalTap II一直以来都是笔者调试Altera FPGA设计的利器,最近比较有时间静下心来研究SignalTap II某些细节,虽然笔者有过不少关于SignalTap的使用,且也发表过一些博文介绍,但是还是有些有技巧如果加以利用是可以大大方便具体项目中的调试。比如本文将要介绍的触发条件位置的选择。

什么是触发位置

所谓触发位置,即trigger position。是指trigger采样位于缓存中的位置,我们知道在设置SignalTap的时候需要设置一个采样深度,缓存深度。那么触发位置的设置(或者说选择)就是指定trigger的位置,或者说指定当trigger发生时缓存数据段的选择。

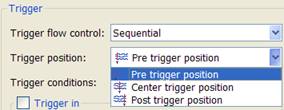

图1:触发位置设置

如图1所示触发位置有三种选择,分别是“Pre trigger position”、“Center trigger position”和“Post trigger position”。这三个设置的意思,很明显就是缓存数据分别选择以trigger前、trigger为中心或者是以trigger后为主。Altera规定Pre,即12%before trigger,88%after;Center,即前后各50%;Post,即88%before,12%after。

实例演示触发位置不同选择

这个设置最大的好处是用户可以在线实时修改选择,而不需要重新编译工程。所以在实际调试工程的时候,找到触发条件后,常常有时候需要看trigger之后的信号情况,而有时候则需要观察trigger之前的状态,有了这个设置就非常方便了。

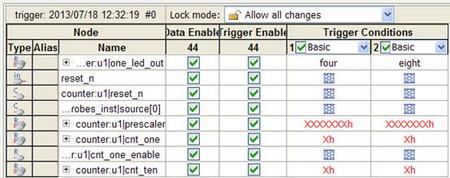

1、 首先我们来看设置为“Pre trigger position”的实例,如图2所示。

![]()

图2

2、 接着我们来看设置为“Center trigger position”的实例,如图3所示。

![]()

图3

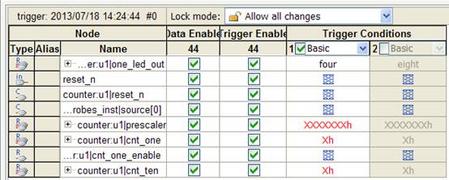

3、 最后我们来看设置为“Center trigger position”的实例,如图4所示。

![]()

图4

结论

大家可以清楚看到图2、图3和图4的异同,相同点是触发的条件设置都是一样的,不同的就是触发后SignalTap显示的数据段不同,图2主要显示trigger 发生之后的数据,图3显示平均展示trigger前后的数据,而图4则主要显是了trigger发生之前的数据。

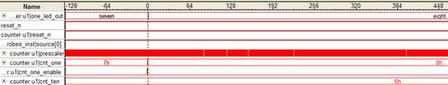

另外,需要注意的是SignalTap最多可以设置10个触发条件(trigger condition),如果设置了多个触发条件,那么触发数据缓存发生必须是所有触发条件都发生,而且存储数据的选择(即trigger position)依据最后一个条件产生。比如图2到图4的实例,笔者设置了两个触发条件,分别是在one_led_out为“four”和“eight”,如图5所示。而数据采集存储是以eight条件触发时为依据。

图5:触发条件设置

![]()

![]()

![]()

图6:放大察看触发位置

图6是为了更清晰地看到触发位置,从而放大了图2,可以看到触发位置位于从“seven”变化到“eight”处,即第二个触发条件“eight”发生时刻。

最后,如果有多个触发条件的时候,当有些触发条件在调试的时候如果不用时,可以disable这些触发条件,如图7所示,将触发条件中的“对号”去掉即可,需要的时候在选上。如图7所示我们去使能第二触发条件,然后重新运行SignalTap,那么获得的结果如图8所示,数据采样存储发生在单个触发条件“four”处。

图7:去使能某个触发条件

图8:采样存储触发发生在“four”时刻

/5

/5

用户1855852 2016-4-1 22:09

用户1856254 2015-10-22 09:57

用户1856254 2015-10-22 09:55