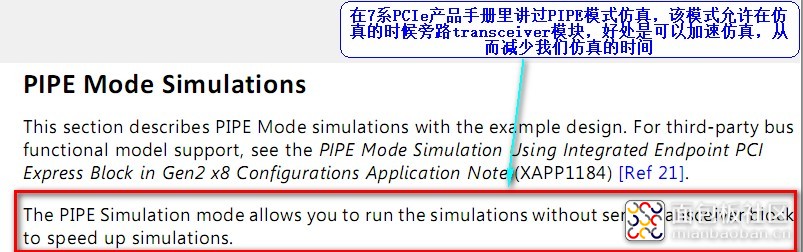

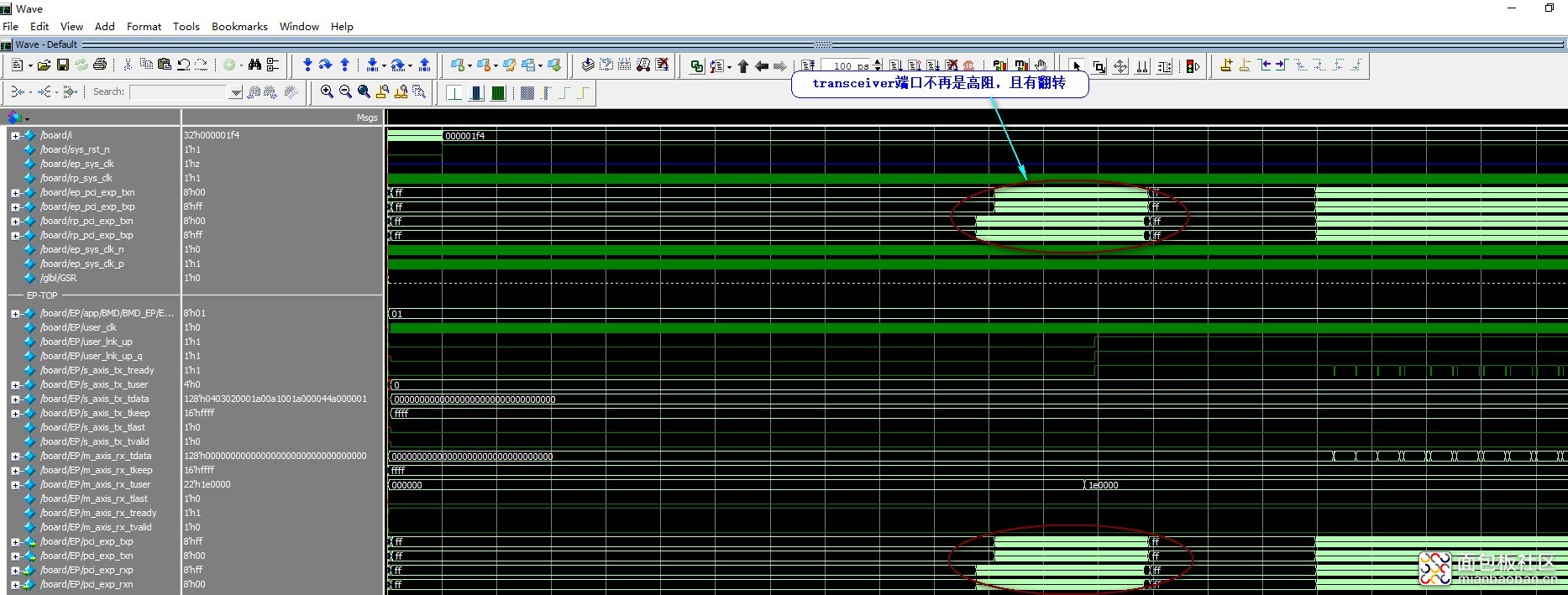

经过查看xapp1052给的参考设计的仿真测试顶层,确实打开了PIPE仿真模式,将PIPE仿真模式关闭后,发现transceiver不再位置高阻,在有PCIe访问的时候,也有数据传递,并能看到数翻转(具体的修改在board.v文件中):

对比打开和关闭PIPE仿真模式,可以发现,打开PIPE模式仿真完成时间只需要50us左右(注:指ModelSim时间),而关闭PIPE,ModelSim跑完整个仿真需要110us(而实际运行的时间可能需要等待近10分钟,关闭PIPE时间可能少于5分钟)。

PS:尽管解决了“高阻态”问题,但是示例给的testname == "pio_writeReadBack_test0"测试仍然没有成功,发现01020304,收到的确实00020304,即收发不匹配。

(备注:vsim +notimingchecks -t 1ps +TESTNAME=pio_writeReadBack_test0 -voptargs="+acc" -L work -L secureip -L unisims_ver \

work.board glbl)

作者: coyoo, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1010859.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

文章评论(0条评论)

登录后参与讨论