在这之前,我一直以为task是不可以综合的,因为自己多是在testbench中使用,而且自己在任务中多使用的是不可以综合的语句,那么采用可综合语句到底可不可以综合了,有何影响了,下面通过一个例子来分析一下。

先看一个实例:

module test_02 (clk,rst_n,dout);

//input & output list

input clk,rst_n;

output [7:0] dout;

reg [7:0]dout;

reg [1:0]cnt;

always @ (posedge clk)

if(!rst_n) cnt <= 2'd0;

else cnt <= cnt + 1'b1;

always @ (posedge clk)

begin

case(cnt)

2'd0 : dout <= 8'h10;

2'd1 : dout <= 8'h01;

2'd2 : dout <= 8'h5a;

2'd3 : dout <= 8'ha5;

default : dout <= 8'h10;

endcase

end

endmodule

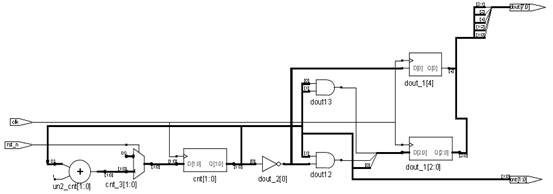

综合后的RTL图如下:

Testbench如下:

`timescale 1ns/1ps

module testbench( ); //测试平台通常没有输入/输出端口

//---输入端口定义为reg和输出端口定义为wire------------------

reg clk,rst_n;

wire [7:0]dout;

wire [1:0]cnt;

//---50M波形----------------------------------------

initial

begin

clk= 1'b0;

forever

#10 clk= ~clk;

end

//---实例引用被测试模块----------------------------------------------

test_02 test_02_0(

.clk(clk),

.rst_n(rst_n),

.cnt(cnt),

.dout(dout)

);

//--监视输出并与期望值做比较--------------------------------------

initial

$monitor("at time is %t and cnt is %d,dout is %d",$time,cnt,dout);

initial

begin

rst_n = 1'b0;

#100;

rst_n = 1'b1;

$display("start simulation right now!");

#100_0000;

end

endmodule

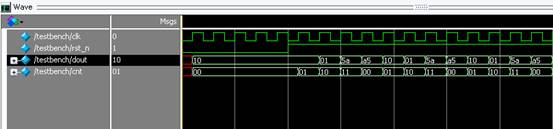

采用modelsim 6.6d的仿真结果如下图:

如下图所示:基本功能是已经实现!也就是一个计数译码的功能。

采用Task来写,则可以采用以下方式:

module test_task01 (clk,rst_n,dout,cnt);

//input & output list

input clk,rst_n;

output [7:0] dout;

output [1:0] cnt;

reg [7:0]dout;

reg [1:0]cnt;

always @ (posedge clk)

if(!rst_n) cnt <= 2'd0;

else cnt <= cnt + 1'b1;

always @ (posedge clk)

begin

code(cnt,dout);

end

//任务的定义

task code;

input [1:0]code_in; //输入代码

output [7:0]dout;

begin

case(code_in)

2'd0 : dout <= 8'h10;

2'd1 : dout <= 8'h01;

2'd2 : dout <= 8'h5a;

2'd3 : dout <= 8'ha5;

default : dout <= 8'h10;

endcase

end

endtask

endmodule

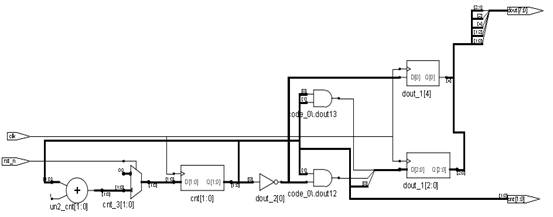

综合后的RTL图如下:

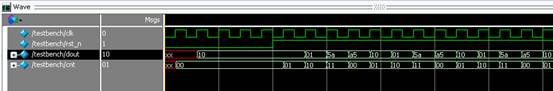

Modelsim的仿真图如下:测试testbench于test_02的testbench相同。

从综合结果来看,二者的综合后的结构是一样的,在功能上也差不多。

如果task能被综合,task只能是采用组合逻辑的语句来实现的,才可以被综合。因为在综合的时候就可以将该组合逻辑部分复制到主程序中去!

用户377235 2013-8-20 13:03

用户1396350 2011-7-19 10:59

用户394057 2011-7-4 23:46

用户85913 2008-3-26 18:06

用户21428 2008-3-23 15:38