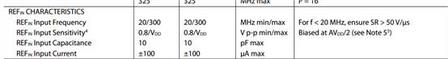

Refer输入

ADF4106的Refer要求不严,正弦波方波都可以通吃(不过考虑到防止误计数,还是建议选择正弦波),输入是高阻抗,而且Vp-p只要求0.8V。记得用隔直电容,这样才能保证被偏置在AVdd/2

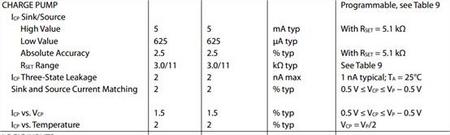

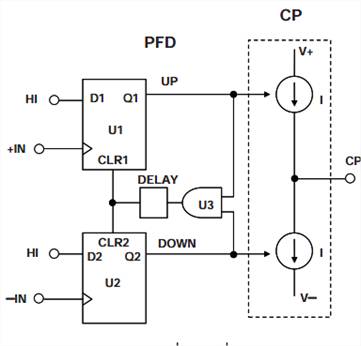

Charge Pump

Charge Pump电流可调,如果用这里的Rset 范围来看,电流范围是289uA到8.5mA,电流越大,在PLL的传递函数里面增益越高,Phase Noise会越好,但是参考杂散会泄露更多

这里有两个指标值的关注,一个是Icp Three-State Leakage,另外一个是Sink and Source Current Matching。这两个指标决定了参考杂散的泄露,PFD频率越高,后者影响越大,前者影响越小。而PLL Lock时,VCO的input电压与Vp/2压差越大,前者影响越大

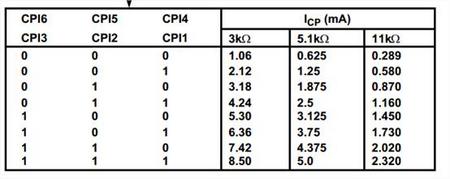

如下面的测试结果

参考杂散

请注意看同样是5800MHz,200KHz的PFD和1MHz的PFD杂散就差了5dB,这说明这时Sink and Source Current Matching占主导地位

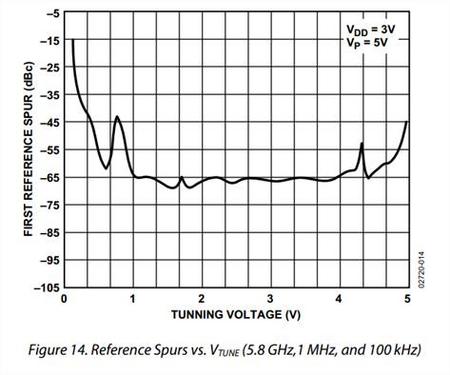

而下面的一个例子,可以说明,Icp Three-State Leakage的影响

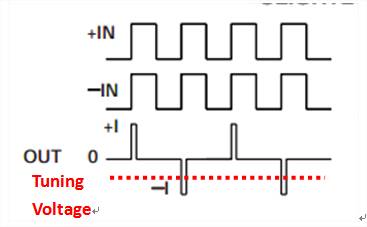

可以看到参考杂散,随着Tuning Voltage在变化。这是因为PLL lock时,高脉冲和低脉冲的平均值会保证在tuning voltage,这个值可以看做是被环路滤波器短暂保持,但是因为Tuning voltage并不和charge pump的三态电压值相同,导致漏电,进而引出参考杂散泄露。压差越大,漏电越厉害,杂散泄露越多

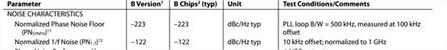

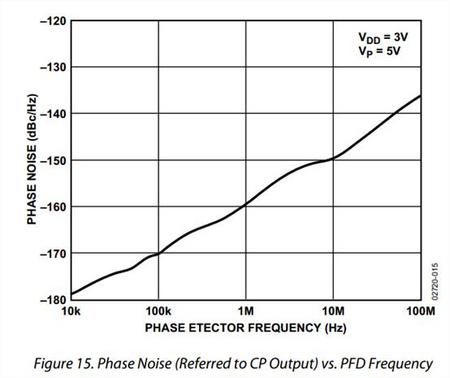

归一化相噪

ADF4106是目前我看到归一化相噪比较好的一颗PLL芯片(NS的很多都是-217以下)

这个归一化相噪可以拿来估计带内相噪,ADIsimPLL也是用这个算的

具体公式如下

PNtot为带内相噪,PNsynth为归一化相噪

这个公式体现了三点:

1. PLL芯片鉴相器本身的相噪与鉴相频率正相关,且对数域是线性

2. PLL反馈放大了鉴相器的相噪,放大倍数是与分频器正相关(是20不是10,因为是电压)

3. 第二条因为乘以20倍,占主导地位

上面这个公式可以把10log Fpfd里面的Fpfd换成与N以及输出频率有关的式子,就可以消去PFD

下一篇预告,ADF4106寄存器,初始化,编程

/5

/5

文章评论(0条评论)

登录后参与讨论