锁相环锁定后的相位问题(二)

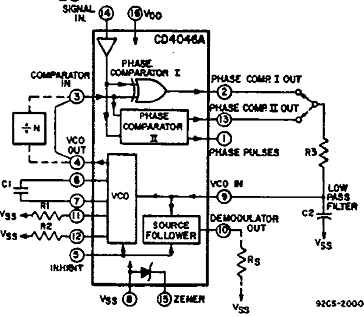

只能继续寻找资料,于是找到了CD4046的datasheet(这个datasheet是扫描版的很不清楚),他的内部结构如下

注意其中有两个鉴相器,上图中的phase comparator I和phase comparator II。在其datasheet中发现对于phase comparator I的说明如下

A second characteristic is that the pahse angle between the signal and the comparator input varies between 0°,180°。

就是说锁定后,输入鉴相器的两个输入信号之间的相位差为0~180°,也就是常数但是每次锁定后都不一样。

而对phase comparator II的说明如下

For phase comparator II,no phase difference exists between signal and comparator input over the full VCO frequency range.

对鉴相器II,在锁定后输入的两个信号的相位差为0。

看来最终的相位关系与鉴相器的类型相关,上图中phase comparator I为一个异或门,而phase comparator II的结构没有给出。

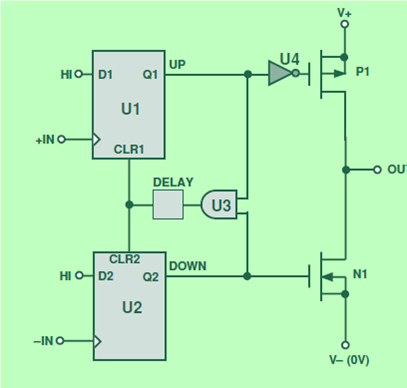

继续查找资料,终于在ADI公司提供的文档《phase locked loops for high-frequency receivers and transmitters—part3》中找到了ADI锁相环中普遍使用的鉴相器,ADI称之为Phase-frequency detector。其简化结构如下

上面的D触发器是上升沿触发的,D1和D2都置高,则(Q1,Q2)的状态为

1)state0:11---都为高,与门U3将两个触发器都清零,进入状态state1

2)state1:00—都为低,这时P1和N1都处于关闭状态。两个触发器CLR为0,处于自由触发状态,就是受+IN和-IN的上升沿触发输出才变为1,更具那个上升沿在前决定进入state2或state3。

3)state3:10—P1打开,N1关闭,输出为V+。

4)state4:01—p1关闭,N1打开,输出为V-。

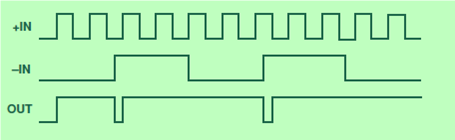

因此当+IN的频率比-IN的频率要高时,如下图

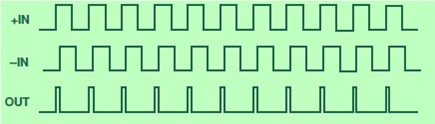

此时OUT大多数时间里都处于V+,控制VCO输出向更高的频率变化。如果+IN比-IN要低,则OUT大多数的时间都处于V-,控制VCO输出向更低的频率变化。直到两个信号的频率一致,如下图

此时频率已经一致,但相位还存在差异。Out为一系列脉冲信号驱动VCO直至+IN和-IN的相位差异为0。

由此可见这种鉴相器其输出是频率差—差异和相位差--差异的函数,通过反馈调整,最终实现了频率和相位的一致,难怪ADI称之为Phase-frequency detector。而前面给出的一般原理解释,给出的是基于模拟乘法器的鉴相器,其输出本质上为频率差-差异的函数,当频率一致后,相位上的差异并不能反映在输出上,因此锁定时只是频率一致而相位不一定一致,存在一个固定的差值,应该称之为frequency detector.

从ADI公司的ADF4106,ADF4110,ADF4210,AD9520,AD9510的datasheet来看都是采用这种Phase-frequency detector。而后一种frequency detector很少使用,只在CD4046上有看到。

在FPGA内部的pll中鉴相器应该也是这种Phase-frequency detector类型,因此才可以实现时钟网络去歪斜功能。

/2

/2

用户444062 2013-7-5 14:14

用户1673212 2013-4-19 13:03

用户620057 2013-4-15 15:36

用户403664 2013-4-12 09:12

转发微博评论 @jackzhu74: 应该在电机控制中是关键参数

@晓宇爸:这要看是分数锁相环还是整数锁相环。整数的没有相差,分数的有随机相差,但可以采用resync模式消除。但是输出如果有buffer,会引入一个固定时延。