ChipScope的两种使用方法

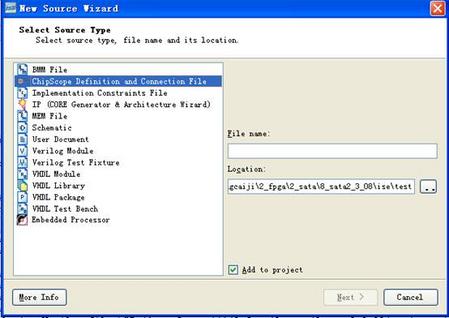

ChipScope是xilinx提供的调试工具,在国内教材中普遍介绍的使用方法都是直接在ise工程中添加相关的ip,如下图

然后综合,添加希望观察的信号。再然后布局布线后,加载到板子上就可以调试了。

我在才开始接触xilinx fpga的时候也是用这种方法,但是发现有些问题:

1) 寻找到某个信号比较困难,原因很多:综合出来的信号网表名和代码里的不符,综合过程将部分逻辑优化为另外一种形式,比如多级寄存器在xilinx fpga中通常被优化成基于LUT的SRL,或者因为有冗余的逻辑,就可能被复用了。当然这些可以通过综合约束来指导XST在综合时避免这些问题,但是有没有其他的办法呢?

2) 特别的触发条件比较难实现:在上面的调用方法中,触发条件比较单一,就是列入在触发信号列表内的信号的组合。如果在调试时,希望触发一个特殊的事件,比如经过一些逻辑判断来触发,由于产生这个触发的逻辑在连入ChipScope之前先要综合,XST往往认为这一部分的逻辑没有用,而直接综合掉了。

3) 如果要观察的信号很多时,每个都手动寻找并添加费时费力。

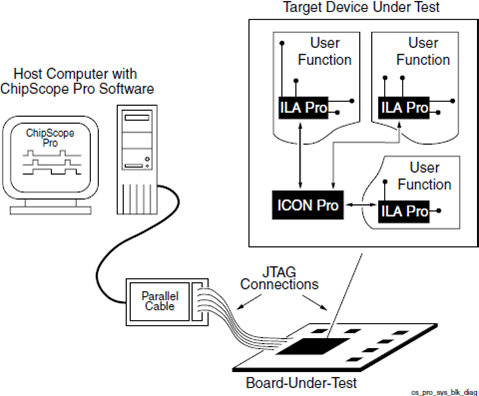

随着使用越来越多的xilinx提供的ip,我发现在官方的代码中ChipScope的调用方法是直接在代码中调用ICON,ILA,VIO及ACT2等核来实现的,这种方法使上面的问题引刃而解。实际上前一种方法调用的ChipScope只是封装这些核而已。那这些核都实现些什么功能:

1) ICON就是用于将其他核和JTAG链相连接的模块,一个工程里面只能有一个ICON,其他所有的包括ILA,VIO,ATC2这些核都要连接在ICON上。最多一个ICON可以连接15个其他的核。

2) ILA核用于采集内部逻辑产生的信号。

3) VIO提供一种双向通道,可以通过JTAG链,在电脑上直接设置内部逻辑的值和读取内部逻辑的值。

4) ACT2适用于外接逻辑分析仪的使用,这个不常用。

5) IBA/OPB,IBA/PLB都是专用与调试包含IBM CoreConnect on-Chip Peripheral Bus和IBM CoreConnect Processor Local Bus的嵌入式项目。这个我也没有用过

6) IBERT用在高速串行接口的调试中,这个在调试GTP,GTX的时候很有用。

我们在实际调试的时候最常用到的就是ICON,ILA和VIO。下面给个图说明他们的连接关系

在实际使用的时候,首先要用xilinx CORE Generator Tool分别产生要调用的核,然后将产生的核添加到工程的VHD文件中,下面是我在调试SATA接口时候的一个例子:

////debug

wire [35:0]CONTROL0;

wire [35:0]CONTROL1;

wire [255:0]DATA;

wire [7:0]TRIG0;

wire [255:0]SYNC_OUT;

icon_ila myicon_ila (

.CONTROL0(CONTROL0), // INOUT BUS [35:0]

.CONTROL1(CONTROL1) // INOUT BUS [35:0]

);

ila_t8_d35 myila_t8_d35 (

.CONTROL(CONTROL0), // INOUT BUS [35:0]

.CLK(clk_75), // IN

.DATA(DATA), // IN BUS [255:0]

.TRIG0(TRIG0) // IN BUS [7:0]

);

chipscope_vio myvio (

.CONTROL(CONTROL1), // INOUT BUS [35:0]

.CLK(clk_75), // IN

.SYNC_OUT(SYNC_OUT) // OUT BUS [255:0]

);

assign DATA[31:0]=fis_fifo_q;

assign DATA[32]=fis_fifo_rd;

assign DATA[33]=fis_fifo_almost_empty;

assign DATA[34]=fis_fifo_empty;

////assign debugdata[7:0]=state;

////assign debugdata[23:8]=tx_data_cnt;

////assign debugdata[27:24]=link_tx_state;

////assign debugdata[28]=receive_dma_act;

////assign debugdata[32:29]=link_rx_state;

////assign debugdata[40:33]=rx_fist_type;

////assign debugdata[63:41]=0;

//assign debugdata[43]=tx_type;

assign DATA[42:35]=debugdata[7:0];

assign DATA[58:43]=debugdata[23:8];

assign DATA[62:59]=debugdata[27:24];

assign DATA[63]= debugdata[28];

assign DATA[67:64]= debugdata[32:29];

…………………………………………….

assign DATA[255:202]=0;

//

assign TRIG0[0]=fis_fifo_rd;

assign TRIG0[1]=link_debugdata[8];

assign TRIG0[2]=link_debugdata[37];

assign TRIG0[3]=debugdata[43];

assign TRIG0[4]=debugdata[44];

assign TRIG0[5]=(fis_fifo_q[31:28]!=0);

assign TRIG0[7:6]=0;

这里ICON连接两个核,分别是ILA和VIO。因此在生成ICON的时候要生成两个CONTROL信号总线分别用于连接myila_t8_d35和myvio。

ILA核用于连接要观察的信号,将需要观察的信号直接连接到DATA数据口上就可以了。不存在找不到信号的情况。这样就避免了在茫茫网标中寻找信号的问题。触发信号也是直接连接上了,但是可以自己添加逻辑作为触发条件的判断,比如

assign TRIG0[5]=(fis_fifo_q[31:28]!=0);

不用担心XST把这段逻辑当成无用的逻辑综合掉了。

VIO设置成输入,信号SYNC_OUT可以控制内部逻辑,触发事件,方便调试。当然也也可以设置成双向,这样可以根据不同的输入获取不同的输出。

还有,如果不同的信号来自不同的时钟域,则可以调用多个ILA分别连接不同的时钟,对应采集不同时钟域的信号,可以保证同时正确分析不同时钟域的事件。

/4

/4

用户1739725 2015-5-11 22:23

用户377235 2015-1-13 17:14

用户377235 2014-9-28 09:12

用户551020 2014-7-17 09:27