锁相环锁定后的相位问题(一)

昨天公司来了一个客户,交谈中论及锁相环。他认为锁相环在锁定后输出的信号与参考信号只是频率相同,而相位上存在一个固定的相位差,并且每次锁定这个相位差都是不同的。也就是说,如下图

在锁定的时候,参考信号Ui(t)与Uo(t)存在一个相位差,关键是这个相位差每次锁定还不一样。

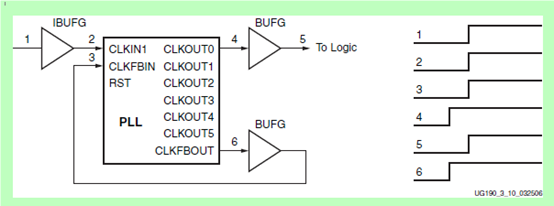

但是这个说法立刻让我想起了在xilinx FPGA中使用PLL时,所使用的一种模式为时钟网络去歪斜,如下图

理想情况下,只要在CLKFBOUT反馈到CLKFBIN的路径上插入一个BUFG,就可以让clkout0输出的时钟经BUFG最后到达目的逻辑(to logic)的相位与FPGA外部引脚输入的参考时钟一致。在上图中就是信号1和5的相位是严格对齐的。这样做的目的是有利于IO引脚的OFFSET时序分析。这种模式的实现前提是,锁定时,信号2和3的相位要达到一致,就是相位差为0。

如果按这位客户的说法,在锁定后信号2和3必然存在一定的相位差,并且每次上电都不同。那上图这个功能是无法实现的。因此这个问题就成了pll内部的鉴相器在锁定时是仅仅频率相同,还是频率和相位都相同。

于是开始上网搜索资料,找到一个正弦波鉴相器的数学模型如下:

![]() 任何一个理想模拟乘法器都可以作为有正弦特性的鉴相器。设输入信号为:

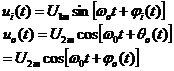

任何一个理想模拟乘法器都可以作为有正弦特性的鉴相器。设输入信号为:

压控振荡器的输出信号为:

|

|

在一般情况下,ωi 不一定等于ωo ,所以为了便于比较两者之间的相位差,现都以ωo t 为参考相位。这样 ui(t) 的瞬时相位为:

|

|

![]() 其中

其中

按上面的新定义,可将式PLL输入、输出信号改写为

|

![]()

![]() 式中 经乘法器相乘后,其输出为

式中 经乘法器相乘后,其输出为

通过环路滤波器,把上式中高频分量滤除。则鉴相器的输出为

|

|

可以看到鉴相器的作用:将两个输入信号的相位差转变为输出电压ud(t)。

由于相位就是频率的积分,因此当相位差为一个恒定的值,则对相位差做微分可得频率差为0,就是锁定状态。

以上是普遍存在教科书中的关于鉴相器的原理说明。从这个论述来看,的确支持客户的说法,但颠覆了我利用pll调试fpga io时序的理论基础。

/4

/4

finelei2002_826889072 2013-9-16 12:20

用户377235 2013-4-12 10:37

用户403664 2013-4-12 08:57