FPGA中数值的计算都是以补码形式进行的。因为对于机器而言,他们只能识别数值0和1,而不能像人脑那样判断符号位,然后判断正负再进行计算。对于原码,补码,反码可以在我收录的一篇文章中学习:

http://bbs.ednchina.com/BLOG_ARTICLE_2114396.HTM

以下我写了个程序来验证数值绝对值的比较:

module minus_judge(clk,rst,

dina,dinb,

result);

input clk,rst;

input[11:0] dina,dinb;

output result;

reg result;

reg[11:0] dina_r,dinb_r;

//计算数据的绝对值

always@(posedge clk or negedge rst) begin

if(!rst) begin dina_r <= 0; dinb_r <= 0; end

else begin

if(dina[11]==1) dina_r <= ~(dina-1'b1);

else dina_r <= dina;

if(dinb[11]==1) dinb_r <= ~(dinb-1'b1);

else dinb_r <= dinb;

end

end

//比较绝对值大小

always@(*) begin

if(dina_r[10:0]>=dinb_r[10:0]) result <= 1;

else result <= 0;

end

endmodule

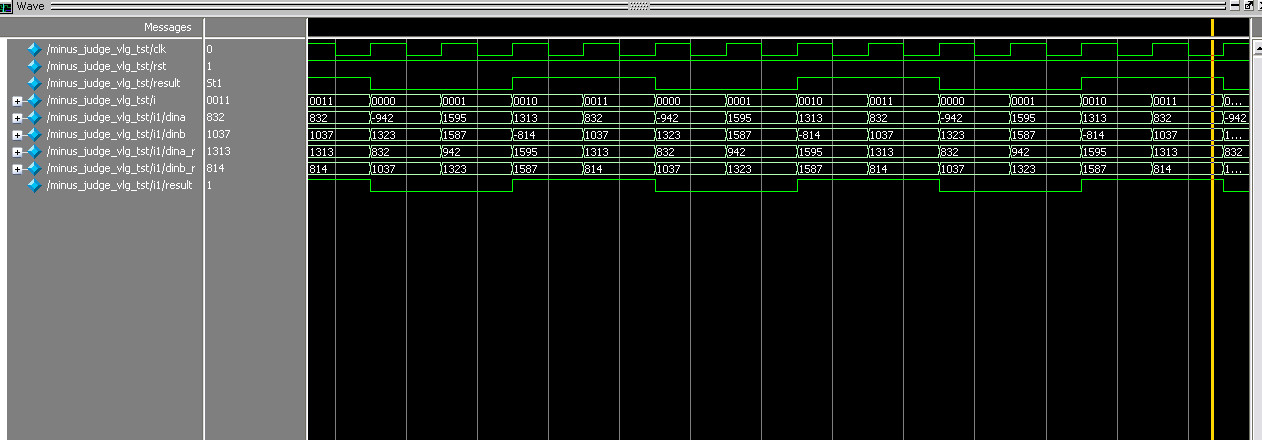

其中的仿真数据输入可以借用verilog的读数据函数readmemh("filename.txt",datamenm)。以16进制读取,个人感觉这样比较方便,16进制显示MATLAB产生也方便。对于负数,在输入时候可以是最高位取反,具体算法是比如我们要产生12位的数据,最高位为符号位,则数据为负数时候需要加上2^12,使得最高位取反,在modelsim中可以以decmal形式查看数据波形。

以下是我的功能仿真图:

/5

/5

用户377235 2013-11-12 22:43

用户408396 2012-5-23 18:45

用户377235 2012-3-20 14:50

用户419715 2012-3-9 18:37