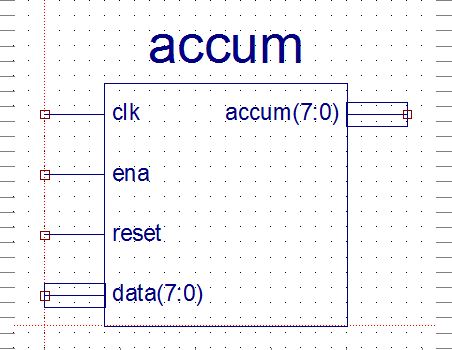

累加器用于存放当前的结果,它也是双目运算其中一个数据来源。复位后,累加器的值是0。当累加器通过ENA口收到来自CPU状态控制器LOAD_ACC信号时,在CLK1时钟上升沿就收到来自于数据总线的数据。累加器模块图如下:

module accum(

input clk,

input ena,

input [7:0] data,

input reset,

output reg[7:0] accum

);

always @(posedge clk)

begin

if(reset)

accum <= 8'h00;

else

if(ena) //当cpu状态控制器发出LOAD_ACC信号

accum <= data;

end

endmodule

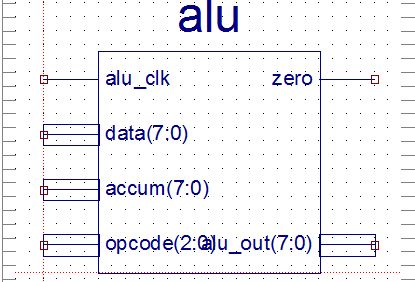

算术运算器是根据输入的8种不同操作码分别实现相应的加、与、异或、跳转等8种基本操作运算。利用这几种基本运算可以实现很多种其他运算以及逻辑判断等操作。算术运算器模块图如下:

module alu(

input alu_clk,

input [7:0] data,

input [7:0] accum,

input [2:0] opcode,

output reg[7:0] alu_out,

output zero

);

parameter HLT = 3'b000,

SKZ = 3'b001,

ADD = 3'b010,

ANDD = 3'b011,

XORR = 3'b100,

LDA = 3'b101,

STO = 3'b110,

JMP = 3'b111;

assign zero = !accum;

always @(posedge alu_clk)

begin

casex(opcode)

HLT: alu_out <= accum;

SKZ: alu_out <= accum;

ADD: alu_out <= data + accum;

ANDD: alu_out <= data & accum;

XORR: alu_out <= data ^ accum;

LDA: alu_out <= data;

STO: alu_out <= accum;

JMP: alu_out <= accum;

default: alu_out <= 8'bx;

endcase

end

endmodule

/3

/3

文章评论(0条评论)

登录后参与讨论