数据控制器

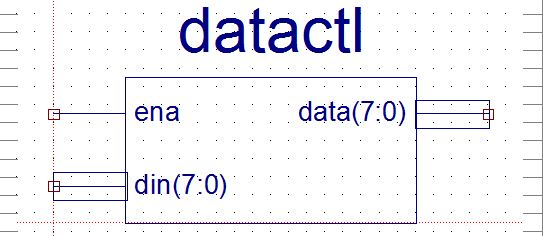

数据控制器的作用是控制累加器数据输出,由于数据总线是各种操作时传送数据的公共通道,不同的情况下传送不同的内容。有时需要传输指令,有时要传RAM区或接口的数据。累加器的数据只有在需要往RAM区或端口写时才允许输出,否则应呈现高阻态,以允许其他部件使用数据总线。所以任何部件往总线上输出数据时,都需要控制信号。而此控制信号的启、停,则由cpu状态控制器输出的各信号控制决定。数据控制器何时输出累加器的数据则由状态控制信号DATACTL_ENA决定。数据控制器模块图如下:

module datactl(

input [7:0] din,

input ena, // 连状态控制器的DATACTL_ENA

output [7:0] data

);

assign data = (ena)?din:8'bzzzz_zzzz;

endmodule

地址多路器

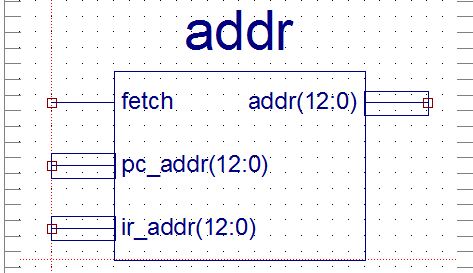

地址多路器用于选择输出的地址是PC地址还是存储器地址。每个指令周期的前4个时钟周期用于从ROM中读取指令,输出的是PC地址;后4个时钟周期用于对RAM的读写,该地址由指令中给出。地址的选择输出信号由时钟信号的8分频信号FETCH提供。模块图如下:

verilog代码如下:

module addr(

input fetch,

input [12:0] pc_addr,

input [12:0] ir_addr,

output [12:0] addr

);

assign addr = fetch? pc_addr : ir_addr;

endmodule

/3

/3

文章评论(0条评论)

登录后参与讨论