程序计数器用于提供指令地址,以便读取指令,指令安地址顺序存放在存储器中。有两种途径可形成指令地址:一是顺序执行的情况,二是遇到要改变顺序执行的情况。例如,执行JMP指令后,需要形成新的指令地址。下面就来详细说明PC地址是如何建立的。

复位后,指令指针为零,即每次CPU重新启动将从ROM的零地址开始读取指令并执行。每条指令执行完需要2个时钟,这时PC_ADDR已经加2,指向下一条指令(因为每条指令占两个字节)。如果正执行的指令是跳转语句,这时CPU状态控制器将会输出LOAD_PC信号,通过LOAD口进入程序计数器。程序计数器将装入目标地址,而不是加2。

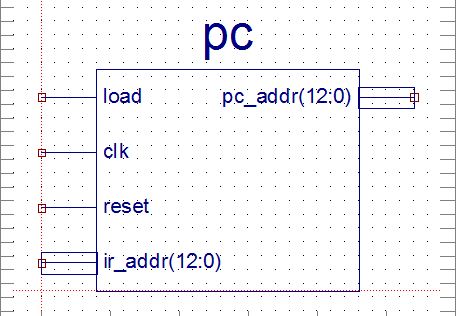

模块图如下:

verilog 程序如下:

module pc(

input [12:0] ir_addr,

input load,

input clk,

input reset,

output reg[12:0] pc_addr

);

always @(posedge clk or posedge reset)

begin

if(reset)

pc_addr <= 13'b0;

else

if(load)

pc_addr <= ir_addr;

else

pc_addr <= pc_addr + 1;

end

endmodule

//参考 夏宇闻·数字系统设计

/3

/3

文章评论(0条评论)

登录后参与讨论