作为恒温控制系统选择的前端温度测量模块,ds18b20的控制相对麻烦点,相关ds18b20的资料可以查看手册。

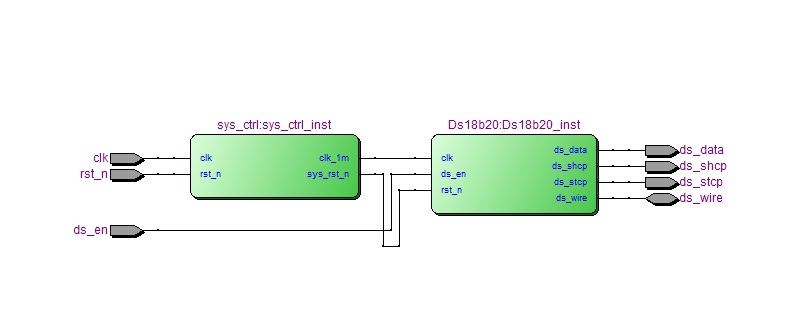

整体模块划分

pll分频模块,25mhz晶振 倍到50 mhz在分频1mhz,1us一个周期,便于ds18b20控制时序。系统时钟选1mhz

ds18b20模块,其中包括ds18b20控制模块,数据转换模块,数码管显示3个模块

我做的比较简单,总线上只挂了一个ds18b20,操作指令顺序

初始化-忽略rom-温度转化-初始化-忽略rom-读寄存器-读出温度-复位。

具体指令和操作步骤参照ds18b20 datasheet。

难点主要是ds18b20的读0,读1 写0,写1时序分开,要求相对比较严格。

每次读写操作都在一个60-70us 的片内。

读1操作的时候,总线先下拉大于1us的时间,释放总线,等待上拉电阻把总线电平拉高,然后控制器采样

读0操作的时候,总线先下拉大于1us时间,释放总线,ds18b20会在总线下拉后15us内给低电平。

注意在读1操作时,控制器的采样必须在总线下拉电平后15us内,具体说来,在进行读1操作时,就是采样时间

必须大于电平拉低时间+电阻把总线电平从低电平拉回高电平,小于总线电平拉低后15us。建议尽量接近15us处。

我这次的设计是读操作开始总线拉低2us后释放总线,采样时间在电平拉低后10us处。

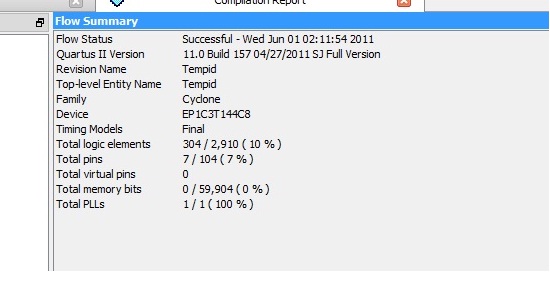

资源消耗情况

实际测量图。和水银温度记温度对于有1-2度误差。手接触ds18b20时候,温度会有明显的上升。

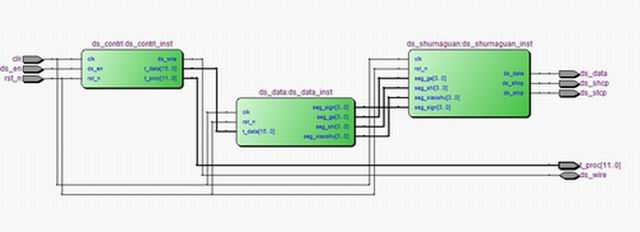

补上一张图~

这是ds18b20控制模块内3个模块,ds_contrl是ds18b20控制模块,ds_data 数据处理模块,t_proc 12位数据时准备送到后面的pid 和模糊算法模块进行处理。

/5

/5

用户589096 2012-6-22 10:30

xucun915_925777961 2011-6-1 10:02