ALTERA公司的CYCLONE V 已经发布,样片已经有了,接下来就会量产,明年就会出现基于CYCON V的开发板。自己关注这个芯片已经有些日子了,现在的资料虽然不是很多,但也正好提前了解一下这个芯片。

CYCLONE V 虽然离我们还远一些,但CYCLONE IV早已经量产了,新的设计完全可以考虑用这个芯片。最近手里在设计两款基于EP4CE15F的开发板,都是关于USB方面的,正好可以验证CYCLONE IV的设计。先说一下FPGA(这里指第四代 CYCLONE IV)与DDR2相关的需要注意的一些问题。

FPGA与外部存储器相关的设计,ALTERA有专门的论述,在其网站上可以找到,http://www.altera.com.cn/literature/lit-external-memory-interface.jsp 。不过,ALTERA提供的与外部存储器相关的资料太多,太繁杂,往往让人摸不到头脑。如果没有半年或者是一年的时间,根本无法去真正设计一块电路板。这里从引脚锁定开始,详述一下DDR2与FPGA相关的设计。

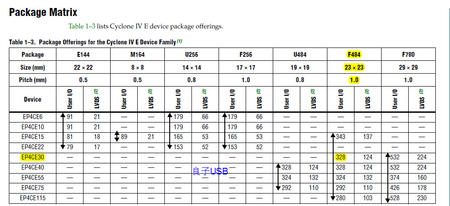

先说一下FPGA的封装,我选择的是BGA封装的EP4CE30,在整个CYCLONE IV中的位置如下:

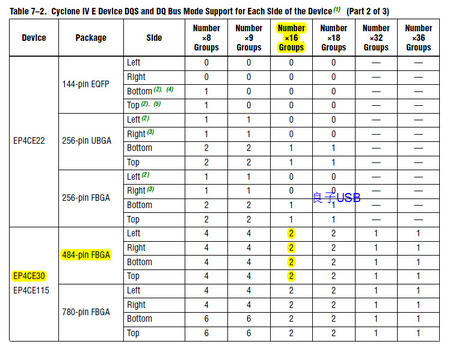

EP4CE30有足够的资料去支持DDR2,我选择的DDR2是16位宽的,下表是EP4CE30 每个边(SIDE)所支持的DDR2的数量。可以看到,每个边支持2个16位数据宽度的DDR2,这样,一片FPGA共四个边,共支持8个DDR2,对一般的应用是足够的了。

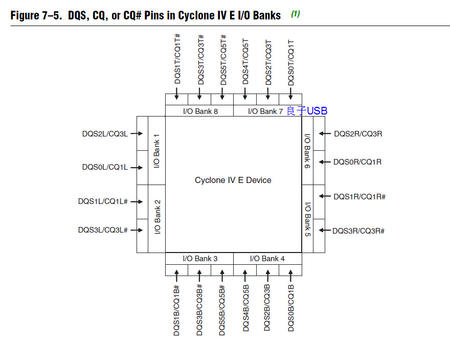

和前几代CYCLONE一样,与外部存储器相关引脚的命名是一致的,如DQSXY,其中DQS代表数据选通信号,X代表DQS组的序号,Y代表这个组所在的边,或者叫侧(SIDE),见下图,

从上图可以看出,左边和右边支持的DQS较少,分别只有4个,而上边和下边则较多,分别有6个。所以在选择FPGA与DDR2相连的边时,建议选择上边(TOP)或者是下边(BOTTOM)。

一个DQS只支持8位的数据DQ,当然也包括与这8位DQ相关连的DM。这三个信号是相关联的,在引脚分配的时候,有很多注意的地方。如最上边的BANK8,含有三个DQS信号,分别是DQS1T、DQS3T、DQS5T,其中DQS1T只能和DQ1T分在一组,而不能与其它线的DQ线组合在一起。

关于差分时钟线,也是有要求的,参考资料中如下的描述: 1、In DDR2 and DDR SDRAM memory interfaces, the memory clock signals (CK and

CK#) are used to capture the address signals and the control or command signals.

2、CK/CK# pins must be placed on differential I/O pins (DIFFIO in Pin Planner) and in

the same bank or on the same side as the data pins. You can use either side of the

device for wraparound interfaces. As seen in the Pin Planner Pad View, CK0 cannot be

located in the same row and column pad group as any of the interfacing DQ pins.

大意是这样:差分时钟线只能锁定在差分IO上,并且与数据线DQ所在的BANK或者边在一起。

其它的部分参见其它博客。

我的博客:http://www.eefocus.com/liangziusb/blog/

我的淘宝店铺:http://shop64171919.taobao.com

良子.2012年 承接USB开发工程 代写USB毕设

QQ:2687652834 392425239

/2

/2

文章评论(0条评论)

登录后参与讨论