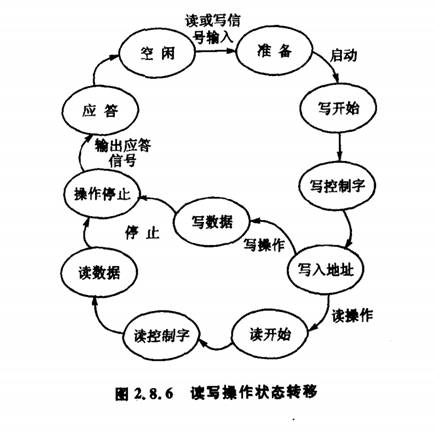

状态机 任务和并行思想

本文主要写了自己对 状态机 任务 并行思想和流水线设计的一些认识

为什么把这几个放在一块写呢

先看一个IIC写EEPROM的代码大致框架吧 通信线为 SDA SCL

Module eeprom_w

//输入输出定义

//变量定义

//参数定义

Assign SDA=(out_***==1)? Sda_buf[7] :1’bz; //控制IIC数据线接收发送

Initial

Begin

//参数初始化

End

Always @(negedge sys_clk) //为iic产生时钟

If(复位)

Scl<=0;

Else

Scl=~scl;

Always @(scl下降沿)

如果复位 初始化某些参数

否则begin

Casex(main_state) //状态机

状态1 空闲 准备跳入下一个状态

状态2 发开始信号 (调用任务) 准备跳入下一个状态

状态3 发设备地址(调用任务) 准备跳入下一个状态

状态4 发数据地址(调用任务) 准备跳入下一个状态

状态5 发数据(调用任务) 准备跳入下一个状态

状态6 发停止信号 (调用任务) 准备跳入下一个状态

状态7 发ACK应答信号(调用任务)准备跳入下一个状态

Default:

Endcase

End

任务1 发送IIC起始信号(代码实现)

任务2 将8位数据发到IIC总线(代码实现)

任务3 从IIC总线上读取8位数据 (代码实现)

任务4 发送IIC结束信号(代码实现)

任务5 发送IIC ack应答信号(代码实现)

Endmodule

因为通过阅读代码发现无论是UART收发器,LCD1206驱动程序还是IIC收发器的实现

1,最清晰明白的实现方法就是使用状态机(看来大部分程序都离不开它)

,2,有状态机的地方就可以通过调用任务 使程序看起来更有调理

,3,而收发器的工作运行都是并行的 我把并行称为随时准备执行 只要收到使能命令立刻执行 比如立即发送FIFO中的数据到uart口 这就是fpga的优势之一吧

状态机:它不是一种电路,而是一种设计思想。我的感觉就是实现任务执行流程的控制 往往用always配合case语句实现。

Moore有限状态机:输出与输入无关,仅依赖于内部状态。

Mealy有限状态机:输出不仅决定于内部状态还跟外部输入有关。

其中要注意状态码的实现,状态码的设计会直接影响使用的逻辑资源数并影响执行速度。

常见的有二进制码00 01 10 11位值变化跨度大,枚举型1 2 3,格雷码0010 0110 0111每次变化一位但是难以理解记忆,独热码00 01 10 010 100每次1向左移动便于观察和理解。

描述方式

1 状态机描述方法

状态机描述时关键是要描述清楚几个状态机的要素,即如何进行状态转移,每个状态的输出是什么,状态转移的条件等。具体描述时方法各种各样,最常见的有三种描述方式:

1、一段式:整个状态机写到一个always模块里面,在该模块中既描述状态转移,又描述状态的输入和输出;

2、二段式:用两个always模块来描述状态机,其中一个always模块采用同步时序描述状态转移;另一个模块采用组合逻辑判断状态转移条件,描述状态转移规律以及输出;

3、三段式:在两个always模块描述方法基础上,使用三个always模块,一个always模块采用同步时序描述状态转移,一个always采用组合逻辑判断状态转移条件,描述状态转移规律,另一个always模块描述状态输出(可以用组合电路输出,也可以时序电路输出)。

一般而言,推荐的FSM 描述方法是后两种。这是因为:FSM和其他设计一样,最好使用同步时序方式设计,以提高设计的稳定性,消除毛刺。状态机实现后,一般来说,状态转移部分是同步时序电路而状态的转移条件的判断是组合逻辑。

关于描述方法看参考(一段式,两段式等)

http://keendawn.blog.163.com/blog/static/888807432011824113626238/

http://wenku.baidu.com/view/ffb87c679b6648d7c1c7466e.html

http://wenku.baidu.com/view/30f2f2dca58da0116c1749e6.html

任务:任务比函数更灵活所以在设计中得到了广泛的使用。

设计时要注意控制任务的执行顺序 执行结束时返回一个信号或修改一个变量

否则执行顺序容易出错.

任务就是一段封装在“task-endtask”之间的程序。任务是通过调用来执行的,而且只有在调用时才执行,如果定义了任务,但是在整个过程中都没有调用它,那么这个任务是不会执行的。调用某个任务时可能需要它处理某些数据并返回操作结果,所以任务应当有接收数据的输入端和返回数据的输出端。另外,任务可以彼此调用,而且任务内还可以调用函数。

任务定义语法:

task <任务名>;

<端口及数据类型声明语句>

<语句1>......

endtask

注意:(1)若任务中含有时延或时间控制的语句,则任务是不可综合的。 (2)其他情况下的函数和任务是可以综合的。

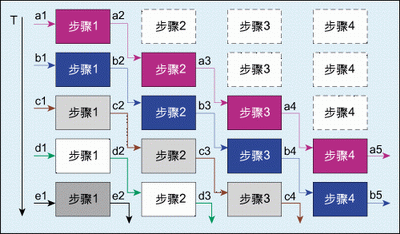

并行与流水线:

这就和C语言的函数调用不一样

C编程中在需要的地方调用一下函数(比如uart发送) 是一步一步顺序执行的

Fpga中任务借助时钟激励随时准备执行 一旦发现使能信号立即执行(比如uart发送使能)

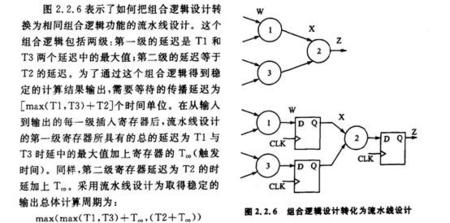

还可以把庞大的任务分解成多个任务 小任务之间添加寄存器

使复杂的逻辑分步完成 减少了每一步的延时

从而使系统的运行频率提高

缺点是耗费了寄存器资源

流水线设计的概念:

所谓流水线设计实际上就是把规模较大、层次较多的组合逻辑电路分为几个级,在每一级插入寄存器组暂存中间数据。K级的流水线就是从组合逻辑的输入到输出恰好有K个寄存器组(分为K级,每一级都有一个寄存器组)上一级的输出是下一级的输入而又无反馈的电路。

/4

/4

文章评论(0条评论)

登录后参与讨论