初学FPGA,觉得还是在学习过程中如果能够把自己的收获和心得给总结出来。那么对自己的学习还是很有必要的。昨天晚上就搞了一个红绿灯的控制,通过一个分频计数程序把20MHz的信号分成1Hz的秒信号,然后通过一个控制模块来控制红绿灯,并且每个灯熄灭的九秒前开始输出数字给数码管译码器 ,

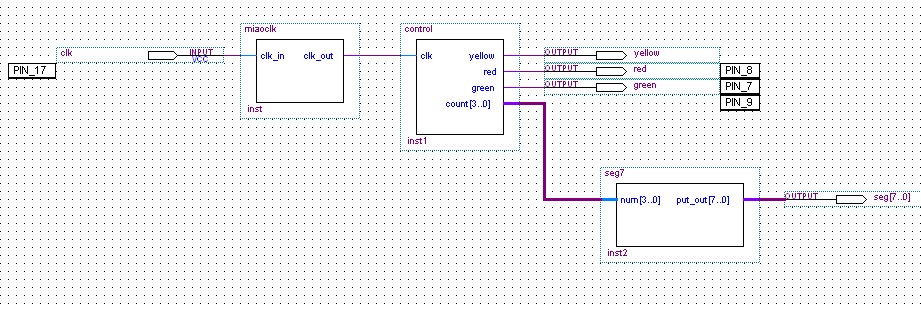

以下就是一个简单的原理图。

分频器的VHDL描述:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity miaoclk is

port (clk_in: in std_logic;

clk_out : out std_logic);

end miaoclk;

architecture func of miaoclk is

constant n :integer :=20000000;

signal clk :integer range 0 to n;

signal temp :std_logic;

begin

process(clk_in)

begin

if(clk_in 'event and clk_in = '1') then

if(clk = n) then

clk <= 0;

temp <= not temp;

else

clk <= clk +1;

end if;

end if;

end process;

clk_out <= temp;

end architecture func;

控制器的VHDL描述

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity control is

port (clk : in std_logic;

yellow,red,green : out std_logic;

count : out integer range 0 to 10);

end control;

architecture func of control is

constant n :integer :=35;

signal acc :integer range 0 to n;

begin

process(clk)

begin

if (clk 'event and clk = '1') then

if (acc = n) then

acc <= 0;

else

acc <= acc +1;

end if;

if (acc < 15) then

green <= '1';

red <= '0';

yellow <= '0';

if (acc>5) then

count <= 15 -acc;

else

count <= 10;

end if;

elsif (acc < 20) then

green <= '0';

red <= '0';

yellow <= '1';

if (acc>15) then

count <= 20 -acc;

else

count <= 10;

end if;

else

green <= '0';

red <= '1';

yellow <= '0';

if (acc>25) then

count <= 35 -acc;

else

count <= 10;

end if;

end if;

end if;

end process;

end architecture func;

数码管译码器的VHDL描述

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity seg7 is

port (num : in integer range 0 to 10;

put_out : out std_logic_vector(7 downto 0));

end entity seg7;

architecture func of seg7 is

begin

process(num)

begin

case num is

when 0 => put_out <= "11111100";

when 1 => put_out <= "01100000";

when 2 => put_out <= "11011010";

when 3 => put_out <= "11110010";

when 4 => put_out <= "01100110";

when 5 => put_out <= "10110110";

when 6 => put_out <= "10111110";

when 7 => put_out <= "11100000";

when 8 => put_out <= "11111110";

when 9 => put_out <= "11110110";

when others => put_out <="00000000";

end case;

end process;

end architecture func;

希望还有大家能够指正或者给出改进。包括程序风格,简化,编写思路之类。。。

/3

/3

文章评论(0条评论)

登录后参与讨论