一:定义

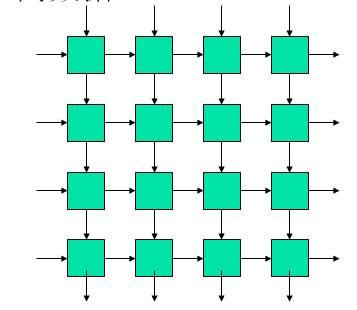

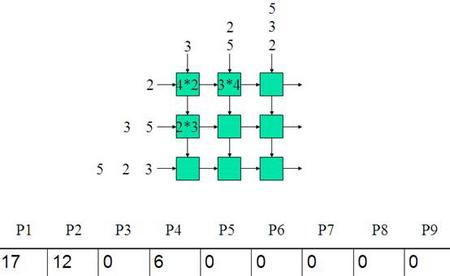

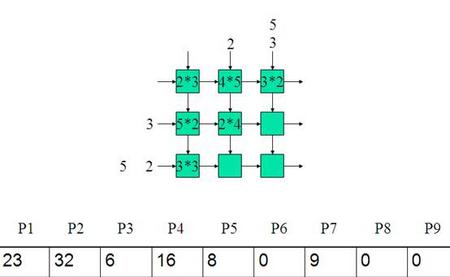

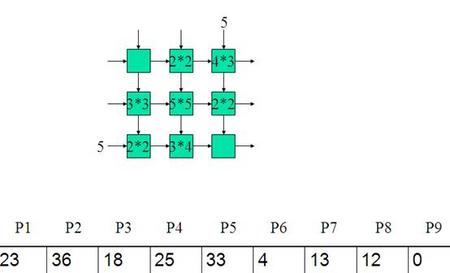

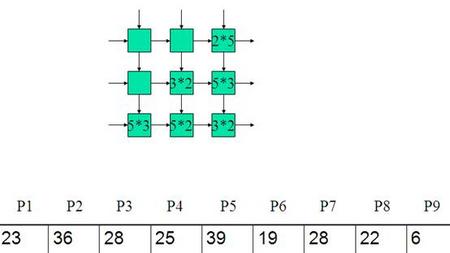

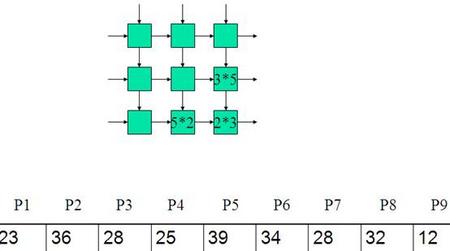

脉动阵列:数据流同步流过相邻的二维阵列单元的处理器结构,一般不同方向流过不同数据。如下图:

二维不同数据在同一时钟下依次输入每个处理单元,而后完成乘法并存在其寄存器中。

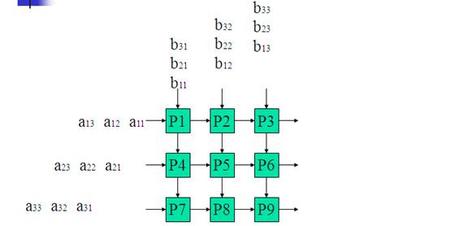

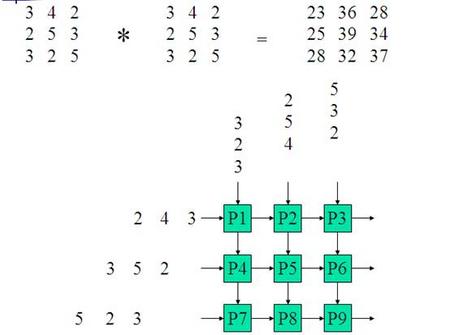

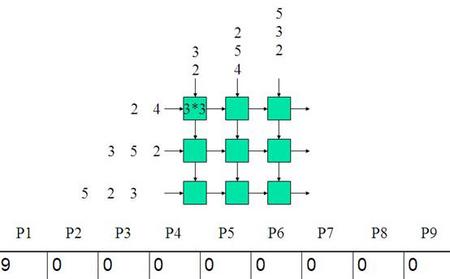

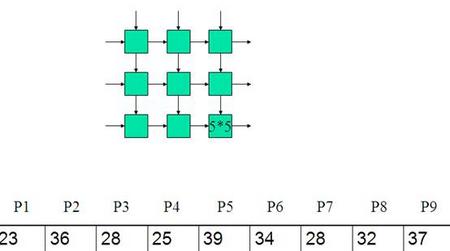

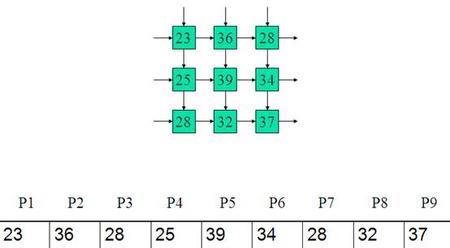

二:举例

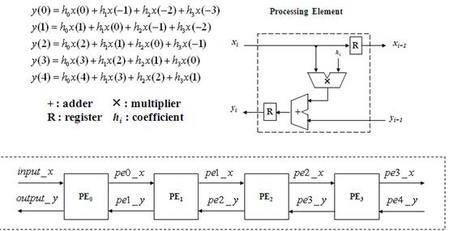

三:设计

结构:

单个PE的代码

module pe(clk, reset, coeff, in_x, in_y, out_x, out_y);

parameter size = 8;

input clk, reset;

input [size-1:0] in_x, coeff;

input [size+size-1:0] in_y;

output [size-1:0] out_x;

output [size+size-1:0] out_y;

reg [size+size-1:0] out_y;

reg [size-1:0] out_x;

always@(posedge clk)

begin

if(reset) begin

out_x <= 0;

out_y <= 0;

end

else begin

out_y <= in_y + (in_x * coeff);

out_x <= in_x;

end

end

endmodule

四个PE,其余类推

//***** main ****************************

module systolic(clk, reset, input_x, output_y);

parameter size = 8;

input clk, reset;

input [size-1:0] input_x;

output [size+size-1:0] output_y;

wire [size-1:0] pe0_x, pe1_x, pe2_x, pe3_x;

wire [size+size-1:0] pe1_y, pe2_y, pe3_y;

wire [size-1:0] h0 = 8'h01;

wire [size-1:0] h1 = 8'h01;

wire [size-1:0] h2 = 8'h01;

wire [size-1:0] h3 = 8'h01;

wire [size+size-1:0] pe4_y = 16'h0000;

pe pe_0(clk, reset, h0, input_x, pe1_y, pe0_x, output_y);

pe pe_1(clk, reset, h1, pe0_x, pe2_y, pe1_x, pe1_y);

pe pe_2(clk, reset, h2, pe1_x, pe3_y, pe2_x, pe2_y);

pe pe_3(clk, reset, h3, pe2_x, pe4_y, pe3_x, pe3_y);

endmodule

/2

/2

用户3919659 2021-6-21 21:16