<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

首先明确数据的收发是由主端口发起的。

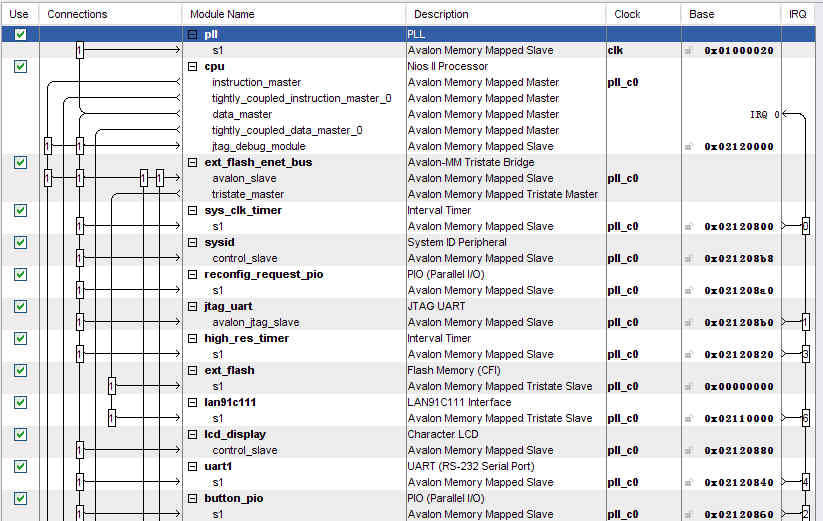

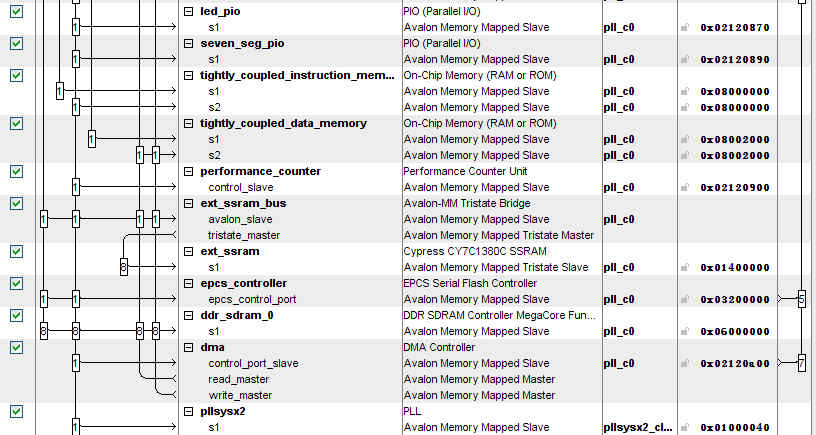

该系统的组成:

CPU: Nios II处理器

存储设备:

ext_flash、

lan<?xml:namespace prefix = st1 ns = "urn:schemas-microsoft-com:office:smarttags" />91c111和对应的三态桥;

紧耦合指令存储器;

紧耦合数据存储器;

SSRAM和对应三态桥;

DDR_SDRAM

外设: 定时器2个(一个为系统时钟,一个为高频时钟精确定时),

sysid,

PIO(按键、LED/、重新配置请求),

JTAG_UART,UART,性能计数器、

EPCS控制器、

DMA控制器,

锁相环(一个产生总线时钟,一个产生外部时钟)

总线->分析(以主端口为源头分析):

CPU-指令主端口:->

JTAG调试从端口、

flash总线三态桥从端口,

ssram总线三态桥从端口,

EPCS控制器从端口

DDR SDRAM控制器从端口

CPU-紧耦合指令主端口->指令紧耦合存储器

CPU-数据主端口->

锁相环

JTAG调试

Flash三态桥

系统时钟定时器

Sysid

JTAG UART

LCD

UART

PIO类型

指令紧耦合存储器

性能计数器

SSRAM三态桥

EPCS控制器

DDR SDRAM

DMA

CPU-紧耦合数据主端口->数据紧耦合存储器

Flash三态桥主端口 -> 外部flash lan91c111

SSRAM三态桥主端口 -> 外部SSRAM

DMA读主端口、写主端口 -> DDR SDRAM SSRAM三态桥 flash三态桥 数据紧耦合存储器

<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />这就是一个SOPC System的架构组成。

/5

/5

ash_riple_768180695 2010-2-4 13:19