内容概括

本书是一本实践性很强的书,从最基础的数字逻辑基础,到最后的片上系统学习。从verilog的基础语法到静态时序分析。本书涵盖了大量的源码,对于一个初学者而言,边看边练,将会很快入门FPGA的开发。

目录

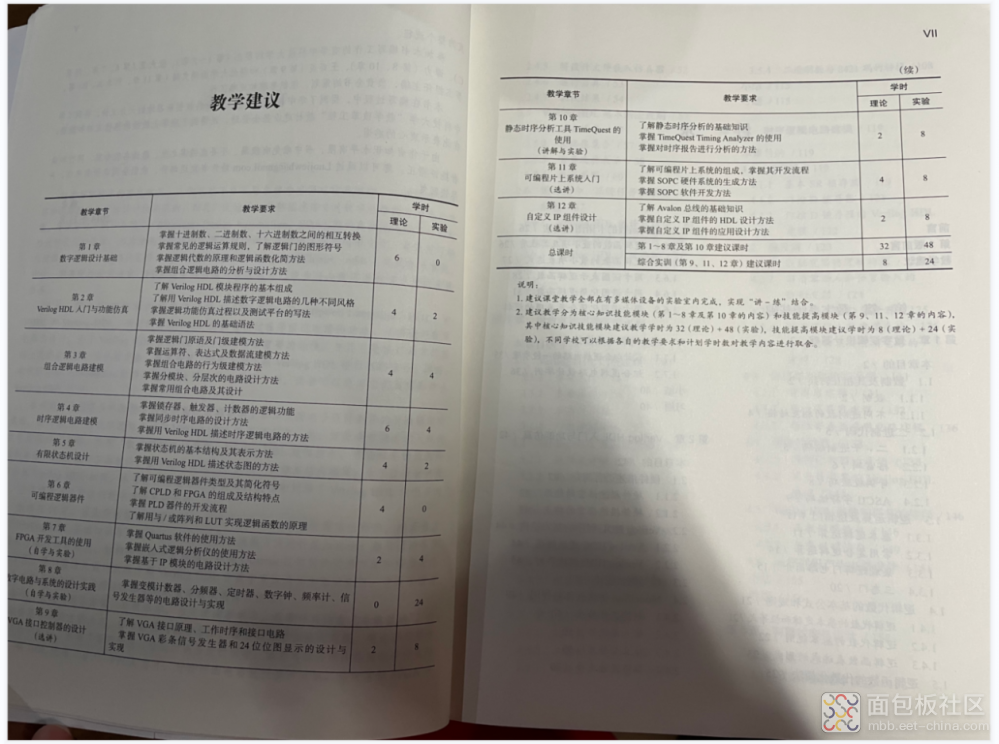

第一章 数字逻辑设计基础

数字设计的入口,在这里认识和掌握数字逻辑设计的思维

第二章 Verilog HDL 入门与功能仿真

FPGA的设计方法很多,最开始的时候,设计师用原理图的方式进行数字设计,小的逻辑可能还能接收,按照现在的逻辑复杂度,还是需要一门语言的-------硬件描述语言。硬件描述语言有两种(verilog和VHDL),这里只说Veriolg,在这章里,将是我们走进硬件逻辑设计的第一步。从语法到简单的逻辑电路,所见即所得,是不是兴趣满满。

第三章 组合逻辑电路建模

分三类展开:门级建模、数据流建模和行为级建模。 进而引出FPGA设计的设计方法:自顶向下。用几个综合案例,继续巩固知识点。循序渐进,简单透彻。

第四章 时序逻辑电路建模

从实现时序逻辑电路的最基本的逻辑单元,到扩展的计数器设计,由浅入深。从简单到复杂。在这里就需要开始写testbench,所以作者这里增加了verilog的系统函数的讲解。安排的井井有条。

第五章 有限状态机设计

从上面的设计中,其实也能看出verilog的程序执行的时候每个块都是并行运行,而有些设计需要逐步运行的。这就体现了有限状态机的重要性。在这章节里,通过阅读将对有限状态机有个深刻的了解。

第六章 可编程逻辑器件

可编程逻辑器件种类很多,每个种类也奠定了FPGA的发展。

第七章 FPGA开发工具的使用

通过这一章对 一款开发工具(quartus)有个简单的掌握

第八章 数字电路与系统的设计实践

在这章节里通过变模计数器、分频器、多功能数字钟以及频率计等7个实例,由简到繁,完美融合数字电路的设计流程与思想。

第九章 VGA接口控制器的设计

早期的时候视频接口相对而言还是比较少的,VGA也是相对比较简单的。虽然目前主流的是HDMI这样的接口,但是视频接口的设计思想和设计基础基本都是相似。通过这一章将对视频接口设计有个简单的认识和设计。

第十章 静态时序分析工具 TimeQuset的使用

经过了上述大量的设计,学生一般还从未考虑过时序的正确性。其实往后,因为设计的复杂性,时序将是FPGA设计最重要的一环。通过这一章,将对quartus集成的TIMEQUSET有个基础的认识和使用。

第十一章 可编程片上系统入门

这一章是选学,片上系统很多,nios是Intel官方的,有个简单了解就差不多了,等用到的时候在深入学习比较好。

第十二章 自定义IP组件设计

FPGA设计的思想是自顶向下。所以会被拆为很多模块,如果将这些模块转换为一种组件,那么后面的设计就跟搭积木一样了。在这章里,将会是这个技能的方法教学。

总评

层层递进,就跟游戏通关打怪一样。从实践入手,培养兴趣,是一本不错的入门好书。

作者: 二月半, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1862109.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论